【 Vivado 】时钟类型

Vivado进行时序分析,对时钟的约束是必不可少的,设计中的时钟可分为一下几种:

- Primary Clocks 主时钟;

- Generated Clocks 衍生时钟;

- Virtual Clocks 虚拟时钟。

Primary Clocks

主时钟一般是FPGA外部芯片如晶振提供的时钟,通过FPGA引脚输入。Vivado进行时序分析时,以主时钟的源端点作为延时计算起始点(0ns点)。主时钟的约束命令如下:

create_clock-name <clock_name> -period <period> -waveform {<rise_time> <fall_time>} [get_ports <input_port>]

下面通过几个实例说明一下约束命令:

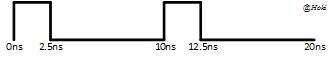

create_clock-name clk_main -period 10 -waveform {0 5} [get_ports GCLK]

周期10ns,0ns上升沿,5ns下降沿。

create_clock-name clk_main -period 10 -waveform {0 2.5} [get_ports GCLK]

周期10ns,0ns上升沿,2.5ns下降沿;与a例周期相同,但是占空比不同,a例中50%,b例中25%。

create_clock-name clk_main -period 20 -waveform {0 10} [get_ports GCLK]

周期20ns,0ns上升沿,10ns下降沿;与a例占空比相同,都是50%,但是周期不同,a例中10ns,b例中20ns。

Generated Clocks

衍生时钟是由设计内部产生,一般由时钟模块(MMCM or PLL)或者逻辑产生,并且对应有一个源时钟,源时钟可以是系统的主时钟或者另外一个衍生时钟。约束衍生时钟时,除了定义周期,占空比,还需要指明与源时钟的关系。通过create_generated_clock命令约束衍生时钟,命令如下:

create_generated_clock -name<generated clock name> -source <master clock source pin or port> -divide_by <div_factor> <pin_or_port>

(图1)

如图1中,主时钟GCLK通过PLL产生两个衍生时钟CLKOUT1和CLKOUT2,其中GCLK—100MHz,CLKOUT1—100MHz,CLKOUT2—10MHz,对于MMCMx, PLLx, BUFR primitives这几种时钟模块,Vivado会自动对主时钟和衍生时钟进行约束。

在Tcl Console中输入report_clocks可以得到时钟报告,以下是未对设计进行任何时钟约束的情况:

report_clocks

INFO: [Timing 38-35] Done setting XDC timing constraints.

INFO: [Timing 38-2] Deriving generated clocks

***************************************************************************

* Report : Clocks

* Design : top

* Part : Device=7z020, Package=clg484, Speed=-1

* Version : Vivado v2013.1 Build 248050 by xbuild on Wed Mar 27 17:27:24 MDT 2013

* Date : Tue Dec 17 12:17:09 2013

***************************************************************************

Attributes

P: Propagated

G: Generated

V: Virtual

I: Inverted

Clock Period Waveform Attributes Sources

clk_in1 10.00000 {0.00000 5.00000} P {GCLK}

clkfbout_clk_gen 10.00000 {0.00000 5.00000}

P,G {clk_gen_u/inst/plle2_adv_inst/CLKFBOUT}

clk_out1_clk_gen 20.00000 {0.00000 10.00000}

P,G {clk_gen_u/inst/plle2_adv_inst/CLKOUT0}

clk_out2_clk_gen 100.00001 {0.00000 50.00000}

P,G {clk_gen_u/inst/ plle2_adv_inst/CLKOUT1}

====================================================

Generated Clocks

====================================================

Generated Clock : clkfbout_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Multiply By : 1

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKFBOUT}

Generated Clock : clk_out1_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Edges : {1 2 3}

Edge Shifts : {0.000 5.000 10.000}

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKOUT0}

Generated Clock : clk_out2_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Edges : {1 2 3}

Edge Shifts : {0.000 45.000 90.000}

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKOUT1}

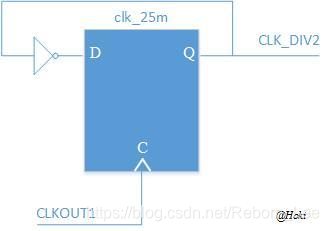

(图2)

如图2中,衍生时钟CLKOUT1通过逻辑产生一个2分频的衍生时钟CLK_DIV2,CLKOUT1的约束已自动生成,对CLK_DIV2约束指令如下:

create_generated_clock -name CLK_DIV2 -source [get_pins clk_gen_u/clk_out1] -divide_by 2 [get_pins clk_25m_reg/Q]

生成的时钟报告如下:

====================================================

Generated Clocks

====================================================

Generated Clock : CLK_DIV2

Master Source : clk_gen_u/clk_out1

Master Clock : clk_out1_clk_gen

Divide By : 2

Generated Sources : {clk_25m_reg/Q}

Generated Clock : clkfbout_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Multiply By : 1

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKFBOUT}

Generated Clock : clk_out1_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Edges : {1 2 3}

Edge Shifts : {0.000 5.000 10.000}

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKOUT0}

Generated Clock : clk_out2_clk_gen

Master Source : clk_gen_u/inst/plle2_adv_inst/CLKIN1

Master Clock : clk_in1

Edges : {1 2 3}

Edge Shifts : {0.000 45.000 90.000}

Generated Sources : {clk_gen_u/inst/plle2_adv_inst/CLKOUT1}

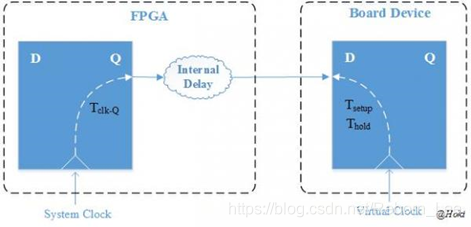

Virtual Clocks

虚拟时钟是在FPGA设计不存在的时钟,但是为什么要引入呢?先看一下图3中结构,FPGA与板上的其它芯片间有数据交互,属于FPGA内部时序单元到输出端口的路径。芯片上的时钟并不是由FPGA提供,Vivado在进行这部分时序分析时并不知道芯片的时钟,因此需要定义一个虚拟时钟,然后约束输出端口的output delay。

约束虚拟时钟的命令也是create_clock,但是其不需要指定-source,如下指令:

create_clock -period 100.000 -name SCLK -waveform {0.000 50.000}

时钟报告如下,定义的虚拟时钟SCLK属性为Virtual,无source。

report_clocks

INFO: [Timing 38-35] Done setting XDC timing constraints.

INFO: [Timing 38-2] Deriving generated clocks

*****************************************************************

* Report : Clocks

* Design : top

* Part : Device=7z020, Package=clg484, Speed=-1

* Version : Vivado v2013.1 Build 248050 by xbuild on Wed Mar 27 17:27:24 MDT 2013

* Date : Tue Dec 17 14:08:19 2013

***************************************************************************Attributes

P: Propagated

G: Generated

V: Virtual

I: Inverted

Clock Period Waveform Attributes Sources

clk_in1 10.00000 {0.00000 5.00000} P {GCLK}

CLK_DIV2 40.00000 {0.00000 20.00000} P,G {clk_25m_reg/Q}

SCLK 100.00000 {0.00000 50.00000} V {}

clkfbout_clk_gen 10.00000 {0.00000 5.00000} P,G {clk_gen_u/inst/

plle2_adv_inst/CLKFBOUT}

clk_out1_clk_gen 20.00000 {0.00000 10.00000} P,G {clk_gen_u/inst/

plle2_adv_inst/CLKOUT0}

clk_out2_clk_gen 100.00001 {0.00000 50.00000}

P,G {clk_gen_u/inst/plle2_adv_inst/CLKOUT1}

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85303619

- 点赞

- 收藏

- 关注作者

评论(0)