【 Vivado 】输入延迟约束(Constraining Input Delay)

前几篇博文提到了四种时序路径:基本的时序约束、分析的概念

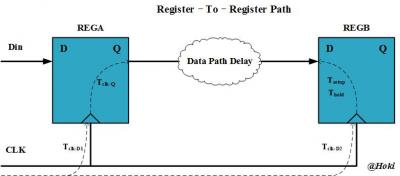

1) FPGA内部时序单元间的路径

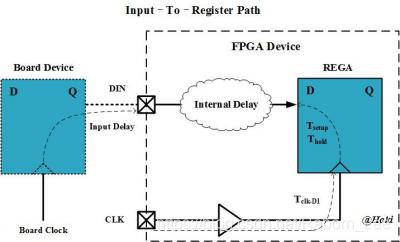

2) 输入端口到FPGA内部时序单元的路径

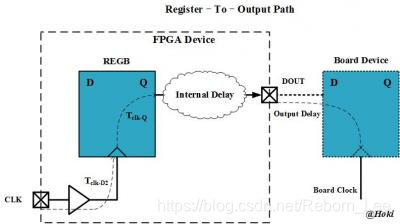

3) FPGA内部时序单元到输出端口的路径

4) 输入端口到输出端口的路径

其中1. FPGA内部时序单元间的路径中,时序分析所需要的时间参数:Tclk-D1, Tclk-Q, Tdata_path_delay, Tclk_D2, Tsetup, Thold已能确定,只要属于FPGA内部的时间参数,Vivado则会根据相应设计计算得到,因此4. 输入端口到输出端口的路径的时间参数也能确定。

其它两条路径都相应缺少FPGA外部的几个时间参数,这些参数都需要通过时序约束告知Vivado,然后Vivado才能精确地进行这些路径的时序分析。这一节先介绍

2. 输入端口到FPGA内部时序单元的路径这条路径的约束。

在输入端口到FPGA内部时序单元的路径中,Input Delay这段路径是在FPGA外部,因此需要约束设置其时间参数,通过set_input_delay约束命令约束,具体如下:

set_input_delay –clock{clk} –max/-min input_delay_value [get_ports {DIN}]

另外根据source clock和destination clock,输入接口可分为以下两种情况:

System Synchronous Input

分析输入端口到FPGA内部时序单元的路径时,当source clock和destination clock来自同一个系统时钟时,称为系统同步输入(system synchronous input)。

如图1所示为系统同步输入,source clock是CLKA,destination clock是CLKB,其中CLKB通过输入端口引入FPGA内部(约束成主时钟),而CLKA引到了FPGA外部的板上芯片,并没有引入到FPGA内部,CLKB是采集输入端口的时钟,因此首先约束CLKB为主时钟,约束如下:

create_clock -name CLKB -period 10 -waveform {0 5} [get_ports {CLKB}]

(图1)

其中Tclkd_ext表示外部时钟源到外部芯片的延时;Tclkd_int表示外部时钟源到FPGA输入端口的延时;Tco表示外部芯片tCO时间;Tbd表示外部芯片输出端口到FPGA芯片的板上延时。

对应max_input_delay和min_input_delay,以上几个时间参数都有max和min值,约束如下:

set_input_delay -clock CLKB -max [Tclkd_ext_max + Tco_max + Tbd_max – Tclkd_int_min] [ get_ports DIN ]

set_input_delay -clock CLKB -min [Tclkd_ext_min + Tco_min + Tbd_min – Tclkd_int_max] [ get_ports DIN ]

Source Synchronous Input

分析输入端口到FPGA内部时序单元的路径时,当destination clock来自外部芯片,即与数据输入同源,称为源同步输入(source synchronous input)。

结构如图2所示,从板上芯片输入到FPGA除了有数据,还有一个随路时钟,是由板上芯片产生的。

(图2)

Input Delay Value:

约束Input Delay分max值和min值,参考图2中时间参数,其中Tcd表示外部芯片时钟输出到FPGA输入端口的延时;Tco表示外部芯片tCO时间;Tbd表示外部芯片输出端口到FPGA芯片的板上延时。Input delay的计算式如下:

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

Clock & Data:

源同步输入的约束相比于系统同步输入的复杂些,其根据时钟与数据的关系,可分为边缘对齐(Edge Aligned Clock&Data)和中心对齐(Center Aligned Clock&Data)两种:

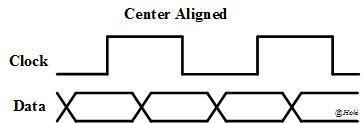

1) Center Aligned

中心对齐是指时钟和数据到达后级时序单元时,时钟沿在数据中心,如图3所示。

在这种情况下可以直接使用时钟采集数据。

(图3)

约束如下:

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) Edge Aligned

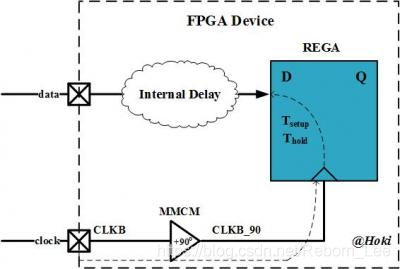

边缘对齐是指时钟和数据到达后级时序单元时,时钟沿与数据变化沿重合,如图4所示。

(图4)

这种情况下显然不满足后级时序单元的Setup要求,因此时钟需要经过一定的移相才能去采集数据,通常采用MMCM模块实现移相,如图5所示。

图(5)

时钟约束如下:

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

create_generated_clock -name CLKB_90 -source [get_clocks CLKB] –phase 90 [get_pins{MMCM|co[0]}]

set_input_delay -clock[get_clocks CLKB_90] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB_90] -min min_input_delay [get_ports indata] -add_delay

SDR & DDR:

源同步接口常用于高速数据传输,如DDR存储器、HyperTransport总线和SPI-4.2标准接口等。其中DDR指双倍速率数据采集(Double Data Rate),在时钟的上升沿和下降沿都传输数据实现双倍速率。

1) SDR(Single Data Rate)

单倍速率数据采集只在时钟的上升沿或者下降沿采集数据,如图6所示。

图6

Input约束只需针对时钟的上升沿或者下降沿进行,如:

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) DDR(Double Data Rate)

双倍速率数据采集在时钟的上升沿和下降沿都采集数据,如图7所示。

(图7)

针对时钟的上升沿和下降沿都需要进行Input约束,如:

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata] -clock_fall -add_delay

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -clock_fall -add_delay

Timing Check in Vivado

以上讲解了如何进行Input delay的约束,可能大家还不明白为什么需要约束input delay?那下面就讲解一下input delay 在时序分析中的作用:

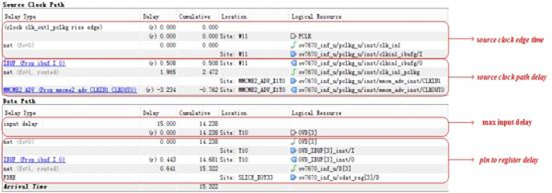

在Vivado中时序分析分为setup check和hold check,其中引入了setup slack和hold slack来界定时序是否收敛。在《2. Timing Basics》中介绍过FPGA内部register_to_register路径setup slack和hold slack的计算方法,本文则介绍一下输入端口到FPGA内部时序单元的路径slack的计算方法,公式如下:

Setup check:

setup slack = data required time – data arrival time

其中:

data required time = destination clock edge time + destination clock path delay

- clock uncertainty

- setup time

data arrival time = source clock edge time + source clock path delay

+ max input delay

+ pin to register delay

为了确认公式的正确性,打开Vivado软件,新建了一个约束了input delay的工程,如下几图所示为中其中一条路径的setup check报告。

约束的时钟周期为40ns,max input delay为15ns

data arrival time= 15.322ns

data required time = 40.199ns

时序报告中slack计算方式与公式完全一致,因此可以得到setup slack = data required time – data arrival time= 40.199ns – 15.322ns = 24.846ns。

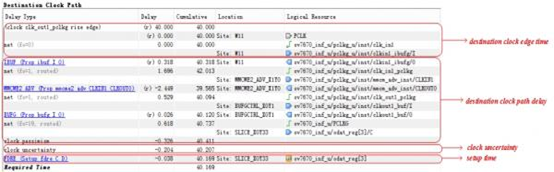

Hold check:

hold slack = data arrival time – data required time

其中

data required time = destination clock edge time + destination clock path delay

+ clock uncertainty

+ hold time

data arrival time = source edge time + source clock path delay

+ pin to register delay

+ min input delay

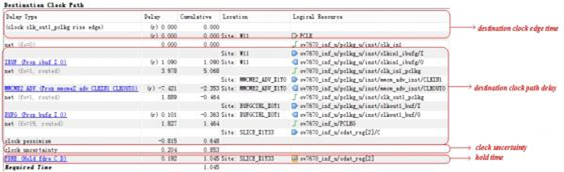

如下几图为Vivado软件分析得到的hold check时序报告:

约束的min input delay = 8ns

data arrival time= 6.474ns

data required time= 1.045ns

时序报告中slack计算方式与公式完全一致,因此可以得到hold slack = data arrival time – data required time= 6.474ns – 1.045ns = 5.429ns。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85304530

- 点赞

- 收藏

- 关注作者

评论(0)