【 FPGA 】玩玩带有异步复位,同步使能的D触发器的两种实现方式

【摘要】 第一种,正儿八经:

带异步复位,同步使能的D触发器:

module dff_reset_en_1seg( input clk, input reset, input en, input d, output reg q ); always @(posedge clk, posedge reset) begin if(reset) q <= 1'b0; else if(...

第一种,正儿八经:

带异步复位,同步使能的D触发器:

-

module dff_reset_en_1seg(

-

input clk,

-

input reset,

-

input en,

-

input d,

-

output reg q

-

);

-

always @(posedge clk, posedge reset)

-

begin

-

if(reset)

-

q <= 1'b0;

-

else if(en)

-

q <= d;

-

end

-

endmodule

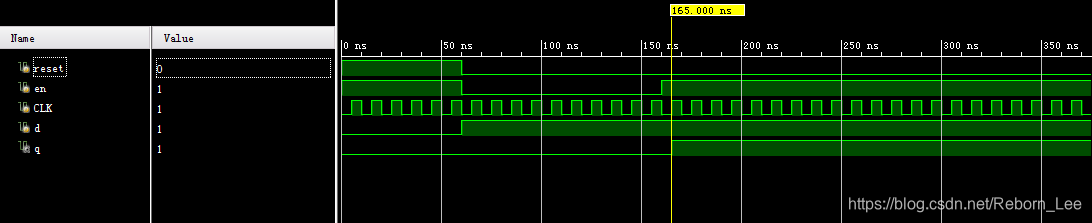

行为测试:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/01/03 10:39:16

-

// Design Name:

-

// Module Name: dff_tb

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module dff_tb;

-

reg reset;

-

reg en;

-

reg CLK;

-

reg d;

-

wire q;

-

-

-

// Note: CLK must be defined as a reg when using this method

-

-

parameter PERIOD = 10;

-

-

always begin

-

CLK = 1'b0;

-

#(PERIOD/2) CLK = 1'b1;

-

#(PERIOD/2);

-

end

-

-

initial begin

-

reset = 1'b1;

-

en = 1'b1;

-

d = 1'b0;

-

-

#60

-

reset = 1'b0;

-

en = 1'b0;

-

d = 1'b1;

-

-

#100;

-

en = 1'b1;

-

d = 1'b1;

-

end

-

-

dff_reset_en_1seg uu1(.clk(CLK), .reset(reset), .en(en),

-

.d(d), .q(q) );

-

-

-

-

-

endmodule

可见,分三个阶段,复位,保持,跟随!

第二种:两段式含异步复位和同步使能的D触发器。

这个触发器没有问题,下面用常规的触发器来实现一个带有异步复位和同步使能的D触发器(练习代码,有点无聊):

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/01/03 10:34:30

-

// Design Name:

-

// Module Name: dff_reset_en_1seg

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module dff_reset_en_1seg(

-

input clk,

-

input reset,

-

input en,

-

input d,

-

output reg q

-

);

-

reg r_reg,r_next;

-

-

always @(posedge clk, posedge reset)

-

begin

-

if(reset)

-

r_reg <= 1'b0;

-

else

-

r_reg <= r_next;

-

end

-

//next-state logic

-

always @*

-

begin

-

if(en)

-

r_next = d;

-

else

-

r_next = r_reg;

-

end

-

-

//output logic

-

always @*

-

q = r_reg;

-

-

-

endmodule

这段代码用于实现同样的功能。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/85682438

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)