【 FPGA 】跨时钟域处理以及边沿检测

【摘要】 本文转载自:跨时钟域处理

题目:多时钟域设计中,如何处理跨时钟域

单bit:两级触发器同步(适用于慢到快)多bit:采用异步FIFO,异步双口RAM加握手信号格雷码转换

题目:编写Verilog代码描述跨时钟域信号传输,慢时钟域到快时钟域

reg [1:0] signal_r;//-----------------------------------------...

本文转载自:跨时钟域处理

题目:多时钟域设计中,如何处理跨时钟域

- 单bit:两级触发器同步(适用于慢到快)

- 多bit:采用异步FIFO,异步双口RAM

- 加握手信号

- 格雷码转换

题目:编写Verilog代码描述跨时钟域信号传输,慢时钟域到快时钟域

-

reg [1:0] signal_r;

-

//-------------------------------------------------------

-

//

-

always @(posedge clk or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_r <= 2'b00;

-

end

-

else begin

-

signal_r <= {signal_r[0], signal_in};

-

end

-

end

-

-

assign signal_out = signal_r[1];

题目:编写Verilog代码描述跨时钟域信号传输,快时钟域到慢时钟域

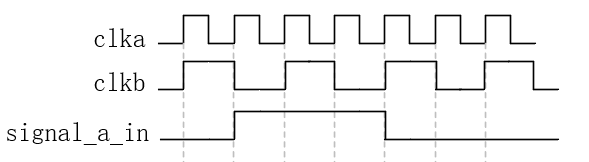

跨时钟域处理从快时钟域到慢时钟域,如果是下面第一个图,clkb则可以采样到signal_a_in,但是如果只有单脉冲,如第二个图,则不能确保采样到signal_a_in。这个时候用两级触发器同步是没有用的。

-

//Synchronous

-

module Sync_Pulse(

-

input clka,

-

input clkb,

-

input rst_n,

-

input pulse_ina,

-

output pulse_outb,

-

output signal_outb

-

);

-

-

//-------------------------------------------------------

-

reg signal_a;

-

reg signal_b;

-

reg [1:0] signal_b_r;

-

reg [1:0] signal_a_r;

-

-

//-------------------------------------------------------

-

//在clka下,生成展宽信号signal_a

-

always @(posedge clka or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_a <= 1'b0;

-

end

-

else if(pulse_ina == 1'b1)begin

-

signal_a <= 1'b1;

-

end

-

else if(signal_a_r[1] == 1'b1)

-

signal_a <= 1'b0;

-

else

-

signal_a <= signal_a;

-

end

-

-

//-------------------------------------------------------

-

//在clkb下同步signal_a

-

always @(posedge clkb or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_b <= 1'b0;

-

end

-

else begin

-

signal_b <= signal_a;

-

end

-

end

-

-

//-------------------------------------------------------

-

//在clkb下生成脉冲信号和输出信号

-

always @(posedge clkb or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_b_r <= 2'b00;

-

end

-

else begin

-

signal_b_r <= {signal_b_r[0], signal_b};

-

end

-

end

-

-

assign pulse_outb = ~signal_b_r[1] & signal_b_r[0];

-

assign signal_outb = signal_b_r[1];

-

-

//-------------------------------------------------------

-

//在clka下采集signal_b[1],生成signal_a_r[1]用于反馈拉低signal_a

-

always @(posedge clka or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_a_r <= 2'b00;

-

end

-

else begin

-

signal_a_r <= {signal_a_r[0], signal_b_r[1]};

-

end

-

end

-

-

endmodule

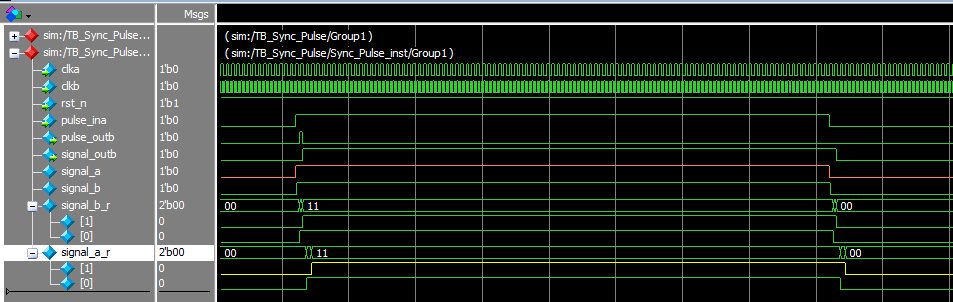

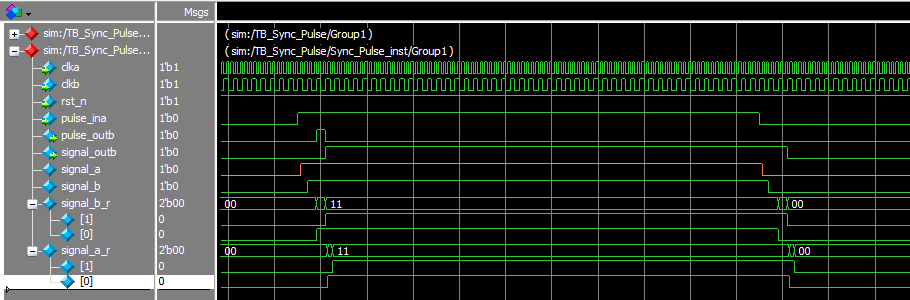

慢到快,单脉冲

慢到快,长信号传递

快到慢,单脉冲

单脉冲,长信号传递

上述代码可以实现快到慢,慢到快时钟域任意转换,pulse_outb会输出单个脉冲,signal_outb输出信号时间长度最少为clkb的四个周期,当signal_a_in的信号长度大于clkb的四个周期,signal_outb输出与signal_a_in时间长度相同。

题目:边沿检测

-

reg [1:0] signal_r;

-

//-------------------------------------------------------

-

//

-

always @(posedge clk or negedge rst_n)begin

-

if(rst_n == 1'b0)begin

-

signal_r <= 2'b00;

-

end

-

else begin

-

signal_r <= {signal_r[0], signal_in};

-

end

-

end

-

-

assign singal_posedge = ~signal_r[1] & signal_r[0];//检测上升沿

-

assign singal_negedge = signal_r[1] & ~signal_r[0];//检测下降沿

记忆:上升沿之前是0,现在变成1,所以上个周期传输到的signal_r[1]是0所以取反。反之亦然。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/88094999

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)