vivado中ILA核的使用

【摘要】 RTL设计

在RTL设计中,将想要抓取的信号前加上: (*KEEP = "TRUE"*) reg led_reg02;

例如,本例中需要抓取的信号是led_reg02;

ILA核的生成及例化

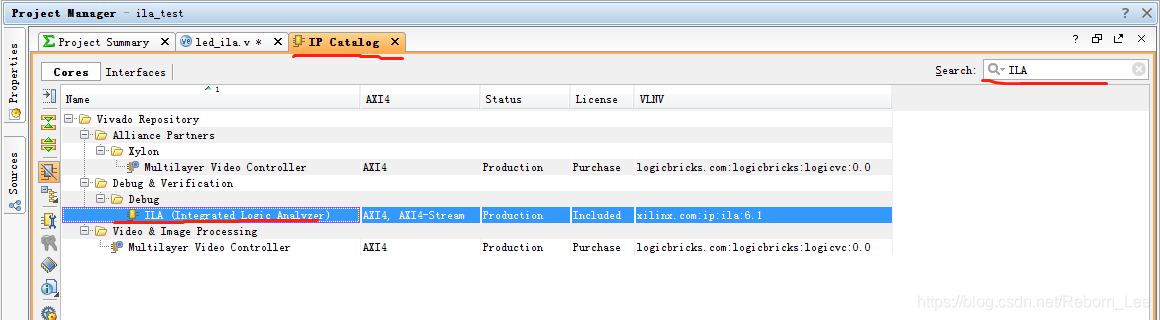

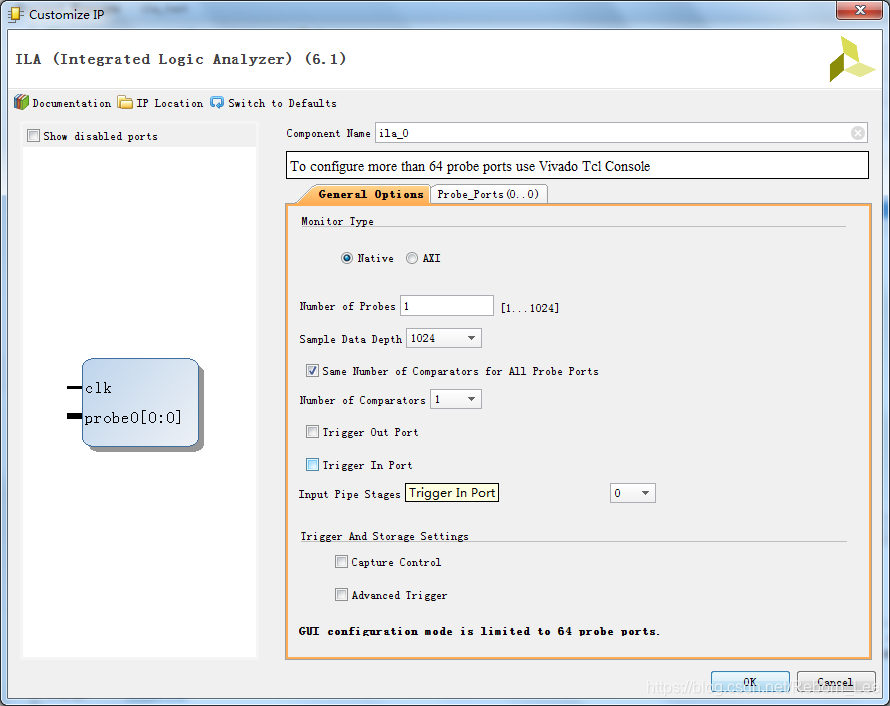

之后生成一个ILA核,如下:

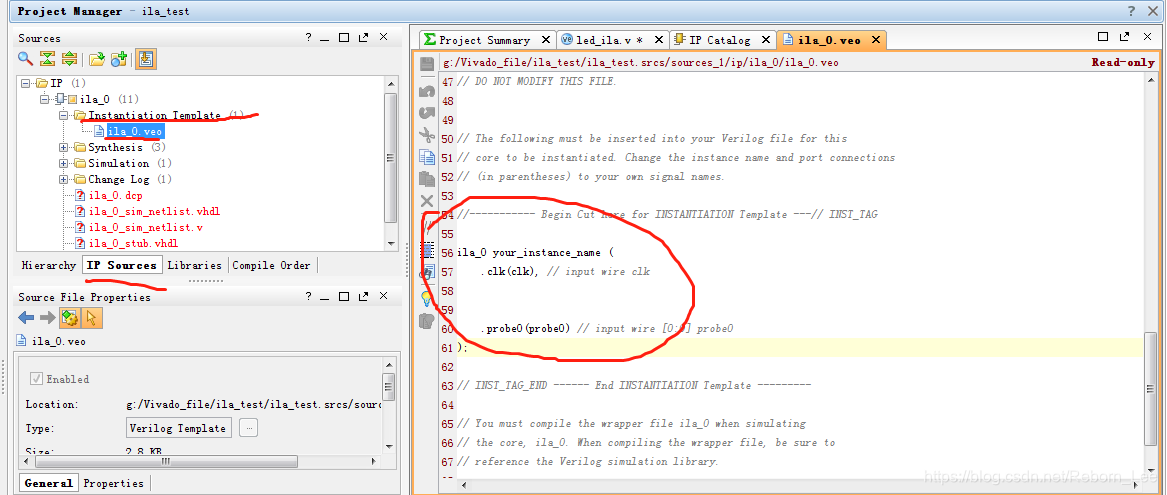

点击OK,生成ILA核完毕。之后在程序中例化ILA核:

给出例化程序部分:

ila_0 ila_s...

RTL设计

在RTL设计中,将想要抓取的信号前加上: (*KEEP = "TRUE"*) reg led_reg02;

例如,本例中需要抓取的信号是led_reg02;

ILA核的生成及例化

之后生成一个ILA核,如下:

点击OK,生成ILA核完毕。之后在程序中例化ILA核:

给出例化程序部分:

-

ila_0 ila_sysclk (

-

.clk(sys_clk), // input wire clk

-

-

-

.probe0(led_reg02) // input wire [0:0] probe0

-

);

我需要抓取的是led_reg02;

sys_clk是系统时钟。

下面进行综合,实现以及生成比特流文件。

下载比特流到FPGA

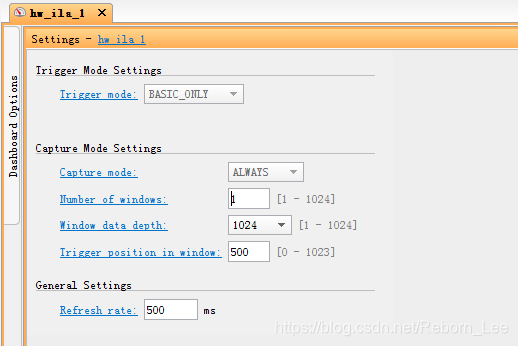

比特流生成之后,对FPGA上电,并打开Hardware Manager:

可以修改设置:

点击触发按钮:

完毕。

本文介绍了一种方便的使用ILA核的方法,当然还有其他的方式,自己去尝试。

参考:

https://blog.csdn.net/qq_38352854/article/details/79502513

http://xilinx.eetop.cn/?action-viewnews-itemid-1282

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/88920770

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)