【Verilog HDL 训练】第 05 天(序列检测)

1. dff和latch有什么区别。

锁存器是一种对脉冲电平(也就是0或者1)敏感的存储单元电路,而触发器是一种对脉冲边沿(即上升沿或者下降沿)敏感的存储电路。

"触发器" 泛指一类电路结构, 它可以由触发信号 (如: 时钟, 置位, 复位等) 改变输出状态, 并保持这个状态直到下一个或另一个触发信号来到时, 触发信号可以用电平或边沿操作.

"锁存器"是触发器的一种应用类型 。强调的是通过触发信号(如时钟)锁存数据输入位。

锁存器是一种脉冲电平敏感的存储单元。最主要的特点是具有使能性的锁存电平功能,即在使能信号有效时,可以锁住输出信号保持不变,而在使能信号失效时,输出与输入相同,等效于一个输出缓冲器。

2. 什么是同步电路和异步电路。

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起

3. 什么是setup time和 hold time。

建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

4. 设计一个101序列检测器。要画出状态转移图,写verilog,并仿真测试。

使用Moore状态机进行序列检测,状态转移图如下:

根据状态转移图,有如下Verilog描述:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/04/26 17:08:22

-

// Design Name:

-

// Module Name: seq_detect

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module seq_detect(

-

input clk,

-

input reset,

-

input din,

-

output reg dout

-

-

);

-

-

localparam s0 = 4'b1110, s1 = 4'b1101, s2 = 4'b1011, s3 = 4'b0111;

-

-

reg [3:0] current_state, next_state;

-

-

always@(posedge clk or posedge reset) begin

-

if(reset) begin

-

current_state <= s0;

-

end

-

else begin

-

current_state <= next_state;

-

end

-

end

-

-

always@(*) begin

-

case(current_state)

-

s0: begin

-

if(din == 1) begin

-

next_state = s1;

-

end

-

else begin

-

next_state = s0;

-

end

-

end

-

s1: begin

-

if(din == 0) begin

-

next_state = s2;

-

end

-

else begin

-

next_state = s1;

-

end

-

end

-

s2: begin

-

if(din == 1) begin

-

next_state = s3;

-

end

-

else begin

-

next_state = s0;

-

end

-

end

-

s3: begin

-

if(din == 1) begin

-

next_state = s1;

-

end

-

else begin

-

next_state = s2;

-

end

-

end

-

default: begin

-

next_state = s0;

-

end

-

-

endcase

-

end

-

-

always@(*) begin

-

if(current_state == s3) begin

-

dout = 1;

-

end

-

else begin

-

dout = 0;

-

end

-

-

end

-

-

-

endmodule

测试文件:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer:

-

//

-

// Create Date: 2019/04/26 17:22:09

-

// Design Name:

-

// Module Name: seq_detect_sim

-

// Project Name:

-

// Target Devices:

-

// Tool Versions:

-

// Description:

-

//

-

// Dependencies:

-

//

-

// Revision:

-

// Revision 0.01 - File Created

-

// Additional Comments:

-

//

-

//

-

-

-

module seq_detect_sim(

-

-

);

-

-

reg clk;

-

reg reset;

-

reg din;

-

wire dout;

-

-

reg [19:0] din_init;

-

integer i;

-

-

initial clk = 0;

-

-

always begin

-

#1 clk = ~clk;

-

end

-

-

initial begin

-

din_init = 20'b1010_0101_0111_0010_1010;

-

reset = 1;

-

-

#11

-

reset = 0;

-

for(i = 0;i < 20;i = i + 1) begin

-

#2

-

din = din_init[i];

-

end

-

-

-

-

end

-

-

seq_detect u0(

-

.clk(clk),

-

.reset(reset),

-

.din(din),

-

.dout(dout)

-

);

-

-

-

-

-

endmodule

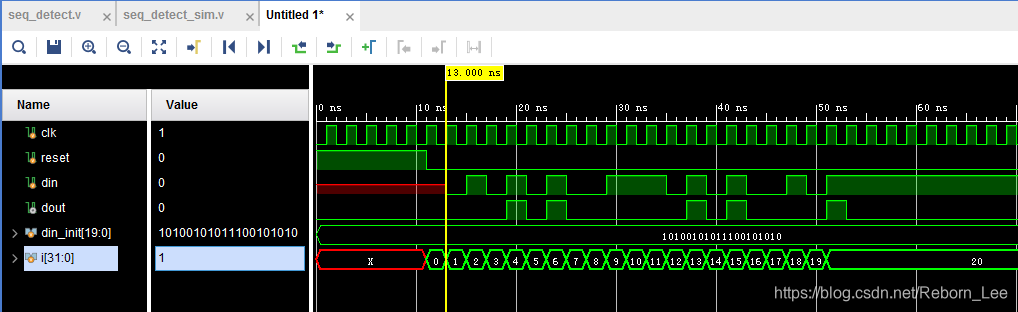

行为仿真时序图:

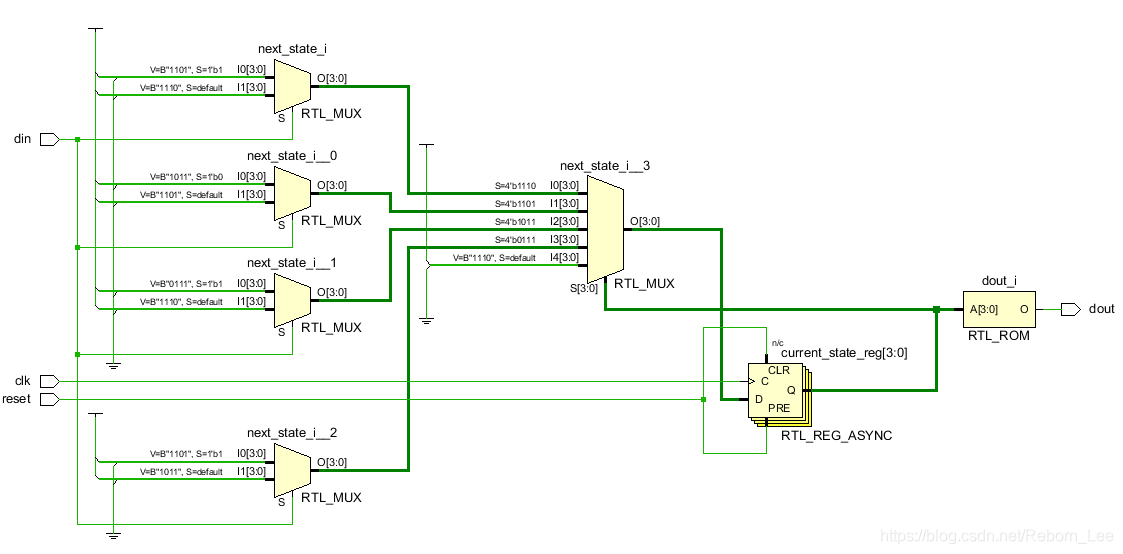

RTL 电路图:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/89556191

- 点赞

- 收藏

- 关注作者

评论(0)