算术运算的RTL代码规则总结

这篇博文是上篇博文:【Verilog HDL 训练】第 12 天(数据通路)的指导规则。

对有符号数以及无符号数运算的一些指导规则。

注:英文为原文,中文为个人认为重要的总结。

1. Signed Arithmetic

• Rule: Use type 'signed' (VHDL, Verilog 2001) for signed/2's complement arithmetic (do not emulate signed arithmetic using unsigned operands/operations). Also, do not use the 'integer' type except for constant values.

对于有符号的补码算术使用类型‘signed’,同时除了常量值,其他都不要使用integer。

• Example: Signed multiplication (Verilog)

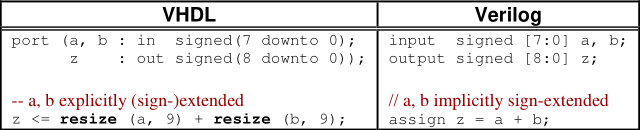

2. Sign-/zero-extension

• Rule: Do not manually sign-/zero-extend operands if possible. By using the appropriate unsigned/signed types correct extension is done in the following way:

VHDL: Use standard functions ('resize' in 'ieee.numeric_std', 'conv_*' in 'ieee.std_logic_arith').

Verilog: Extension is automatically done.

不要人为的进行符号或者零扩展操作;

Verilog中扩展自动完成。

3. Mixed unsigned/signed expression (Verilog)

• Rule: Do not mix unsigned and signed types in one expression.

不要再一个表达式中混合使用有符号以及无符号类型。

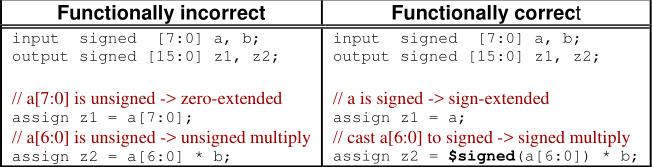

4. Signed part-select / concatenation (Verilog)

• Note: Part-select results are unsigned, regardless of the operands. Therefore, part-selects of signed vectors (for example, "a[6:0]" of "input signed [7:0] a") become unsigned, even if part-select specifies the entire vector (for example, "a[7:0]" of "input signed [7:0] a").

无论什么操作,部分选择后是无符号的。因此对于有符号的向量,部分选择后也是无符号的。

• Note: Concatenation results are unsigned, regardless of the operands.

连接也是如此。

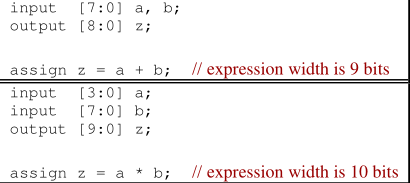

5. Expression widths (Verilog)

• Note: The width of an expression in Verilog is determined as followed:

o Context-determined expression: In an assignment, the left-hand side provides the context that determines the width of the right-hand side expression (that is, the expression has the width of the vector it is assigned to).

也就是说,表达式有它所赋值的向量的宽度。

o Self-determined expression: Expressions without context (for example, expressions in parenthesis) determine their width from the operand widths. For arithmetic operations, the width of a self-determined expression is the width of the widest operand.

自定义表达式:没有上下文的表达式(例如括号中的表达式)从操作数宽度确定它们的宽度。对于算术运算,自定义表达式的宽度是最宽操作数的宽度。

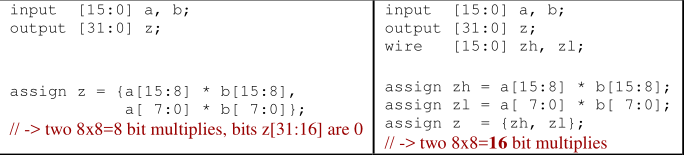

o Special cases: Some expressions are not self-determined even though they appear to be. The expression then takes the width of the higher-level context (for example, left-hand side of an assignment).

Example: Concatenation expression (Verilog).

• Rule: Avoid using self-determined expressions. Use intermediate signals and additional assignments to make widths of arithmetic expressions unambiguous (context-determined expressions).

Guidelines for QoR

更多规则参考:Coding Guidelines for Datapath Synthesis

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/90259514

- 点赞

- 收藏

- 关注作者

评论(0)