【Verilog HDL 训练】第 12 天(数据通路)

【摘要】 数据通路。

y = func(a,b)

func可以是加法,减法,乘法,比较,移位,舍入,饱和等。

分别针对有符号数,无符号数的情况。

提示:可以参考synopsys的一篇文档 https://t.zsxq.com/QF6QNju

加法:

对于无符号数而言:

module arithmetic( input [3:0] a, input [3:0] b, ou...

数据通路。

y = func(a,b)

func可以是加法,减法,乘法,比较,移位,舍入,饱和等。

分别针对有符号数,无符号数的情况。

提示:可以参考synopsys的一篇文档 https://t.zsxq.com/QF6QNju

加法:

- 对于无符号数而言:

-

module arithmetic(

-

input [3:0] a,

-

input [3:0] b,

-

output [4:0] res_sum, //加

-

output [3:0] res_sub, //减

-

output [7:0] res_pro, //乘

-

//output [3:0] res_comp, //比较

-

output [3:0] right_shift //右移

-

);

-

-

-

assign res_sum = a + b;

-

assign res_sub = a - b;

-

assign res_pro = a * b;

-

//assign res_com =

-

assign right_shift = a>>3; //逻辑右移

-

-

wire [3:0] right_shift_a; //算术右移结果

-

assign right_shift_a = a>>>3;

-

-

-

endmodule

-

测试文件:

-

module arithmetic_tb(

-

);

-

-

-

reg clk;

-

reg [3:0] a;

-

reg [3:0] b;

-

wire [4:0] res_sum; //加

-

wire [3:0] res_sub; //减

-

wire [7:0] res_pro; //乘

-

//wire [3:0] res_comp, //比较

-

wire [3:0] right_shift; //右移

-

-

initial begin

-

clk = 0;

-

forever

-

# 2 clk = ~clk;

-

-

end

-

-

initial begin

-

a = 4'b1011;

-

b = 4'b1001;

-

#10

-

a = 4'b1001;

-

b = 4'b0111;

-

end

-

-

-

arithmetic u0(

-

.a(a),

-

.b(b),

-

.res_sum(res_sum),

-

.res_sub(res_sub),

-

.res_pro(res_pro),

-

.right_shift(right_shift)

-

);

-

-

-

endmodule

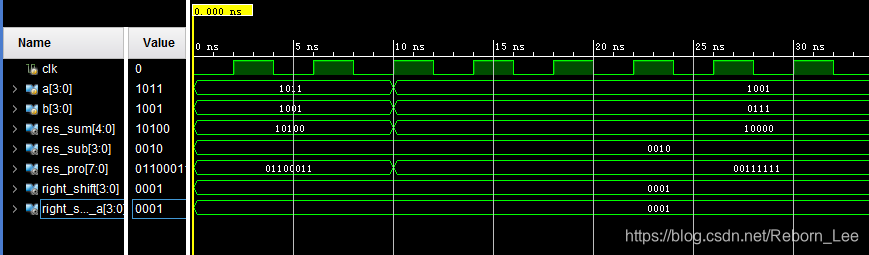

行为仿真时序图:

对于无符号数,逻辑右移和算术右移是一样的,都是高位补零。

- 对于有符号数而言:

-

module arithmetic(

-

input signed [3:0] a,

-

input signed [3:0] b,

-

output signed [4:0] res_sum, //加

-

output signed [3:0] res_sub, //减

-

output signed [7:0] res_pro, //乘

-

output signed [3:0] right_shift //右移

-

);

-

-

assign res_sum = a + b;

-

assign res_sub = a - b;

-

assign res_pro = a * b;

-

//assign res_com =

-

assign right_shift = a>>3; //逻辑右移

-

-

wire [3:0] right_shift_a; //算术右移结果

-

assign right_shift_a = a>>>3;

-

-

-

endmodule

测试文件同上!

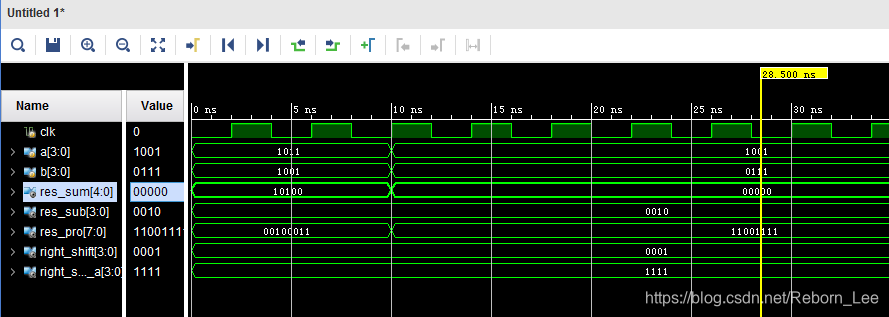

仿真波形:

可以看出,对于有符号数,逻辑右移和算术右移结果不一样,逻辑右移依然是补零,算术右移则补符号位。

但对于有符号数的加法规则如何?

例如上述仿真:1001 + 0111 为什么等于 00000?

也就是-1 + 7 = 0?

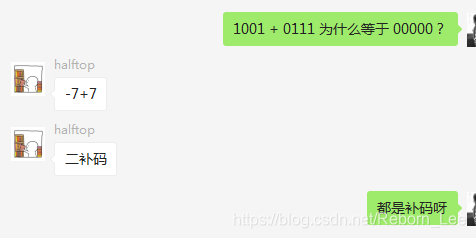

得到了答案:

1001是补码的形式,原码是1111,也就是-7,这样的话就是-7+7=0,也符合道理了。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/90246023

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)