【FPGA】单端口RAM的设计(异步读、异步写)

前面有博文写了同步读写和异步读、同步写的单端口RAM设计:

这篇博文讲异步读写:

在博文:【FPGA】单端口RAM的设计(异步读、同步写)中已经对异步读与同步读进行了比较,这篇博文要对同步写和异步写做一个比较:

首先是代码上的区别:易知,所谓异步写,也就是不依赖于时钟的写,只要给一个地址,且写使能有效(当然片选也得有效)就可以写一个数据:

// Memory Write Block

// Write Operation : When we = 1, cs = 1

always @ (address or data or cs or we)

begin : MEM_WRITE

if ( cs && we ) begin

mem[address] = data;

end

end

异步读自然也是如此:

// Memory Read Block

// Read Operation : When we = 0, oe = 1, cs = 1

always @ (address or cs or we or oe)

begin : MEM_READ

if (cs && !we && oe) begin

data_out = mem[address];

end

end

话不多说,给出Verilog描述:

-

`timescale 1ns / 1ps

-

//

-

// Create Date: 2019/05/28 20:10:21

-

// Design Name:

-

// Module Name: ram_sp_ar_aw

-

//

-

module ram_sp_ar_aw (

-

address , // Address Input

-

data , // Data bi-directional

-

cs , // Chip Select

-

we , // Write Enable/Read Enable

-

oe // Output Enable

-

);

-

parameter DATA_WIDTH = 8 ;

-

parameter ADDR_WIDTH = 8 ;

-

parameter RAM_DEPTH = 1 << ADDR_WIDTH;

-

-

//--------------Input Ports-----------------------

-

input [ADDR_WIDTH-1:0] address ;

-

input cs ;

-

input we ;

-

input oe ;

-

-

//--------------Inout Ports-----------------------

-

inout [DATA_WIDTH-1:0] data ;

-

-

//--------------Internal variables----------------

-

reg [DATA_WIDTH-1:0] data_out ;

-

reg [DATA_WIDTH-1:0] mem [0:RAM_DEPTH-1];

-

-

-

-

-

//initialization

-

-

// synopsys_translate_off

-

integer i;

-

initial begin

-

for(i=0; i < RAM_DEPTH; i = i + 1) begin

-

mem[i] = 8'h00;

-

end

-

end

-

// synopsys_translate_on

-

-

-

//--------------Code Starts Here------------------

-

-

// Tri-State Buffer control

-

// output : When we = 0, oe = 1, cs = 1

-

assign data = (cs && oe && !we) ? data_out : 8'bz;

-

-

// Memory Write Block

-

// Write Operation : When we = 1, cs = 1

-

always @ (address or data or cs or we)

-

begin : MEM_WRITE

-

if ( cs && we ) begin

-

mem[address] = data;

-

end

-

end

-

-

// Memory Read Block

-

// Read Operation : When we = 0, oe = 1, cs = 1

-

always @ (address or cs or we or oe)

-

begin : MEM_READ

-

if (cs && !we && oe) begin

-

data_out = mem[address];

-

end

-

end

-

-

endmodule // End of Module ram_sp_ar_aw

从Verilog描述中可以看出,由于是异步读写,所以根本就没有用到时钟,所以,测试文件中也不存在时钟,给地址就读写完事了。

给出测试文件:

-

`timescale 1ns / 1ps

-

//

-

// Create Date: 2019/05/21 16:00:12

-

// Design Name:

-

// Module Name: ram_sp_ar_sw_tb

-

//

-

-

-

module ram_sp_ar_aw_tb(

-

-

);

-

-

reg [7 : 0] address; // address Input

-

wire [7 : 0] data; // Data bi-directional

-

reg cs; // Chip Select

-

reg we; // Write Enable/Read Enable

-

reg oe; // Output Enable

-

-

reg [7 : 0] data_in;

-

assign data = (cs && we && !oe) ? data_in : 8'dz;

-

-

integer i;

-

-

-

-

initial begin

-

-

cs = 1'b0;

-

we = 1'b0;

-

oe = 1'b0;

-

address = 8'd0;

-

data_in = 8'h00;

-

#20

-

#4 begin//read

-

cs = 1'b1;

-

oe = 1'b1;

-

end

-

-

for (i = 0; i < 256; i = i + 1) begin

-

#4

-

address = i;

-

end

-

-

#4 begin//write

-

we = 1'b1;

-

oe = 1'b0;

-

end

-

-

for (i = 0; i < 256; i = i + 1) begin

-

#4 begin

-

address = i;

-

data_in = data_in + 1;

-

end

-

end

-

-

#4 begin//read

-

we = 1'b0;

-

oe = 1'b1;

-

end

-

-

for (i = 0; i < 256; i = i + 1) begin

-

#4

-

address = i;

-

end

-

-

#4

-

cs = 1'b0;

-

//#100 $finish;

-

#100 $stop;

-

-

-

-

-

-

-

end

-

-

-

ram_sp_ar_aw u_ram(

-

.address(address) , // address Input

-

.data(data) , // Data bi-directional

-

.cs(cs) , // Chip Select

-

.we(we) , // Write Enable/Read Enable

-

.oe(oe) // Output Enable

-

);

-

-

-

endmodule

-

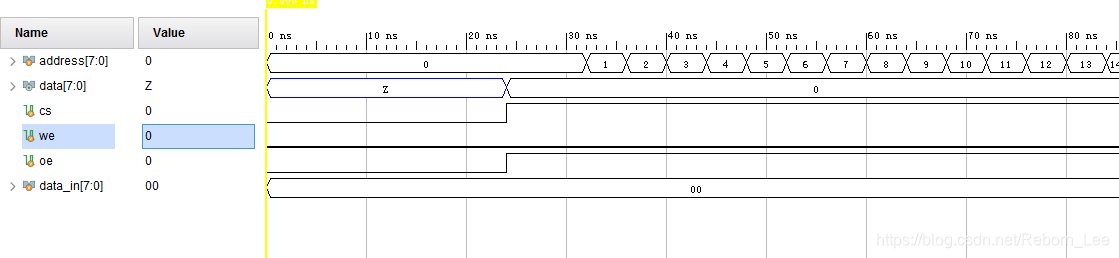

读初始值:

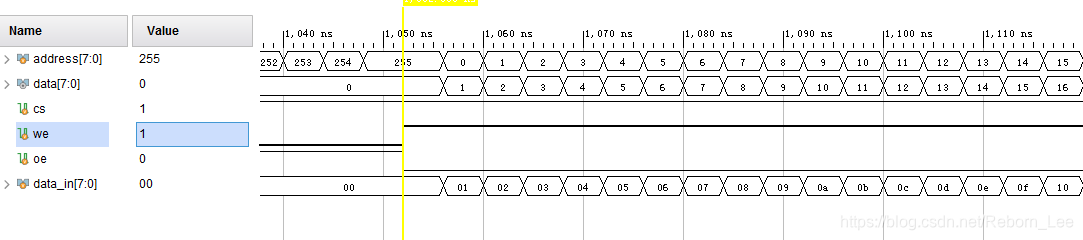

写数据:

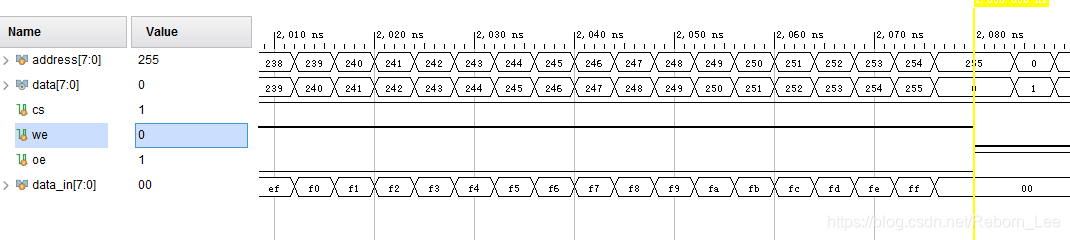

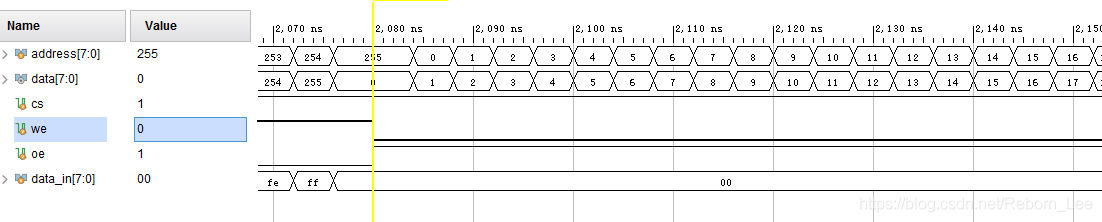

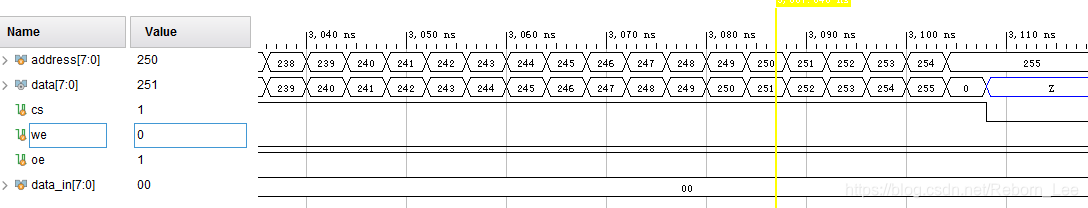

把写进去的数据读出来:

参考文献:

前面已经给出几篇

Single Port RAM Asynchronous Read/Write

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/90646285

- 点赞

- 收藏

- 关注作者

评论(0)