遇见BUG(4)不要默认电平标准!

纠错是一个很考验耐心与运气的事情,有时候真的让你怀疑人生。

最近,我再做一个SRIO以及Auraro 通信的事情,使用了Xilinx提供的例程,可是就是这个看似权威的例程,出现了一些让我感觉“莫名其妙”的错误,搞得一头雾水。

今日,就讲讲这个错误是如何解决的吧。

错误一:

[DRC NSTD-1] Unspecified I/O Standard: 10 out of 16 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: led0[7:0], sys_rst, and sim_train_en.

[DRC UCIO-1] Unconstrained Logical Port: 16 out of 16 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: led0[7:0], sys_clkp, sys_clkn, sys_rst, srio_rxn0, srio_rxp0, srio_txn0, srio_txp0, and sim_train_en.

这里的提示看起来吓死个人,但是稍微有点Vivado调试经验的人,就会明白这是引脚约束的问题,看第一个:Unspecified I/O Standard

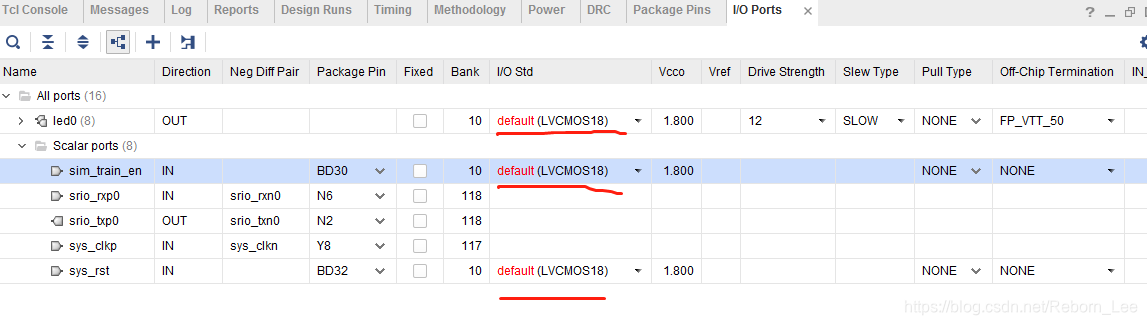

这意思是未指定IO电平标准,打开Implementation中的IO Planning看看是否如此:

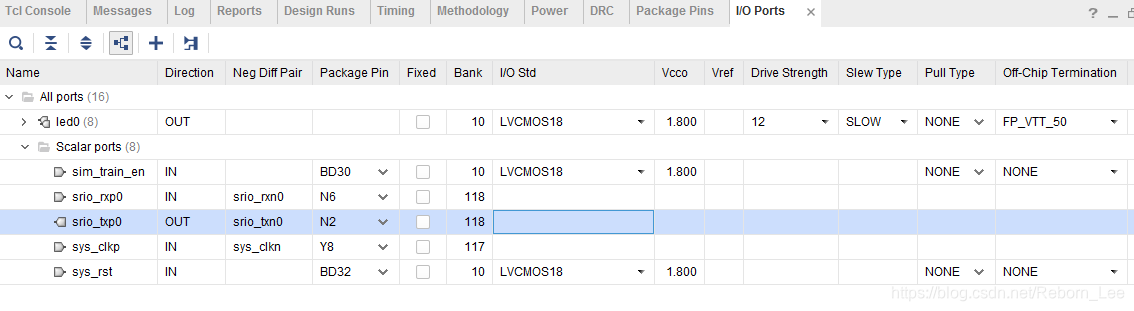

确实如此,那么我们改正它:

改好保存下即可。

刚刚只是改了其中之一的提示,看看另一个提示:

Unconstrained Logical Port

同样,它的意思是未约束的逻辑端口。

这就奇了怪了,也是令我糊涂到写这篇博文之前的一个问题,我明明给了各个逻辑端口位置约束了呀,在之前的几天,我始终不知这到底是什么问题,我甚至怀疑Vivado不智能,乱jr提示。

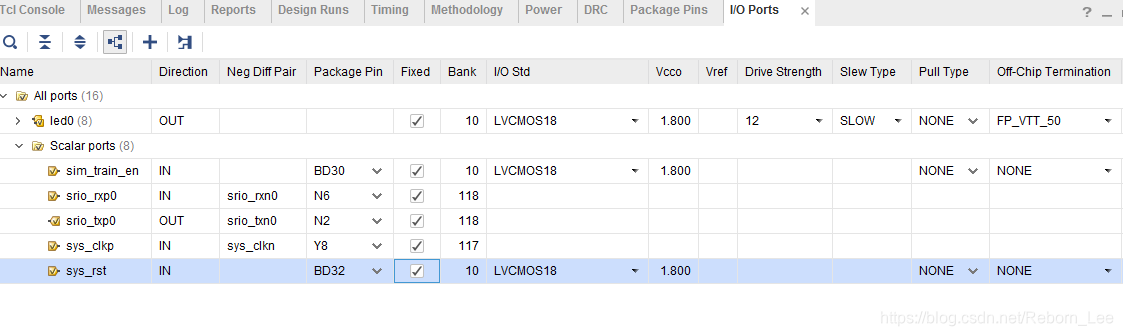

哈哈,此刻明白,虽然约束了位置,但是你并没有选择FIXed呀。

这就像你做了约束,让你确定一样,你没有确定,自然不算。

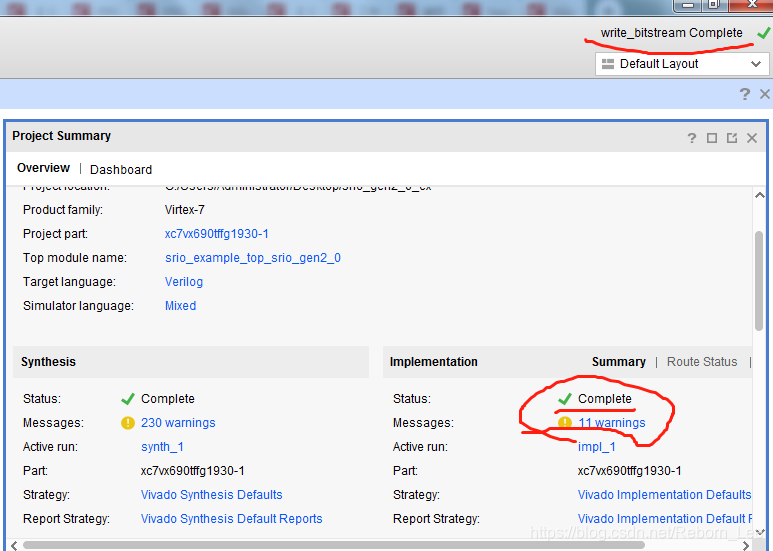

选择之后,保存下,生成bitstream试下。

如果没有其他错误,按理说,这个问题已经解决了。

还有一种错误提示,在这里做出解释:

[Common 17-69] Command failed: This design contains one or more cells for which bitstream generation is not permitted:

<encrypted cell> (<encrypted cellview>)

<encrypted cell> (<encrypted cellview>)

<encrypted cell> (<encrypted cellview>)

If a new IP Core license was added, in order for the new license to be picked up, the current netlist needs to be updated by resetting and re-generating the IP output products before bitstream generation.

这是使用高速串口IP常出现的问题,原因是使用了加密的IP核,Xilinx对这些“核心技术”提供了限制,使用这些IP核必须付费,当然网上也有各种乱七八糟的破解License,但是真的管用吗?

还真管用!厉害厉害。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/90815139

- 点赞

- 收藏

- 关注作者

评论(0)