IC/FPGA校招笔试题分析(一)

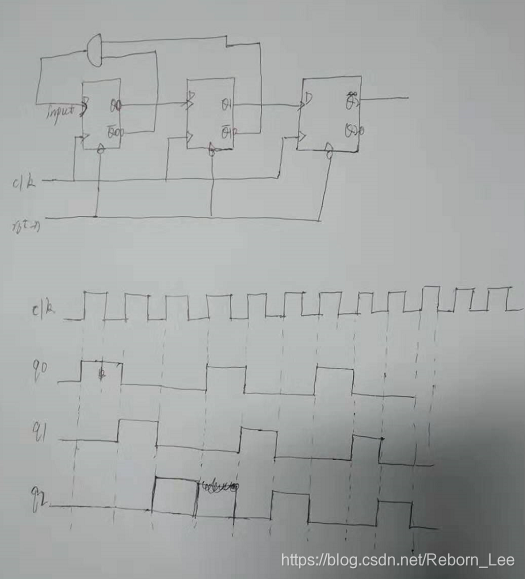

【摘要】 某发科的一个题目,仅仅给出下面一个电路图,让你画出Q1,Q2以及Q3的波形,并描述电路功能。

可以看出,这个电路很简单(可tm的当时就是没做出来),我当时疑惑的是初值是什么,输入初值是什么?

可想想和输入初值有个毛线关系呀,第一个触发器的输入是第二个以及第三个触发器的输出的反馈,是Q1与Q2的或非;

只要触发器复位有初值即可,一般触发器复位初值为0,这里也默认为0,...

某发科的一个题目,仅仅给出下面一个电路图,让你画出Q1,Q2以及Q3的波形,并描述电路功能。

可以看出,这个电路很简单(可tm的当时就是没做出来),我当时疑惑的是初值是什么,输入初值是什么?

可想想和输入初值有个毛线关系呀,第一个触发器的输入是第二个以及第三个触发器的输出的反馈,是Q1与Q2的或非;

只要触发器复位有初值即可,一般触发器复位初值为0,这里也默认为0,那么输入值在复位时应该为1.

那么当正常运行(复位无效)时,q0的第一个值为复位值延迟一拍并持续一个时钟,之后q1、q2就简单了。

为了清晰的分析这个问题,我们把这个电路用Verilog描述出来,之后验证。

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer: reborn lee

-

//

-

// Create Date: 2019/07/24 19:57:47

-

// Design Name:

-

// Module Name: test

-

-

//

-

-

-

module test(

-

input rst_n,

-

input clk,

-

output out2

-

-

);

-

-

wire in1;

-

-

reg q0, q1, q2;

-

-

always@(posedge clk or negedge rst_n) begin

-

if(!rst_n) begin

-

q0 <= 1'b0;

-

q1 <= 1'b0;

-

q2 <= 1'b0;

-

end

-

else begin

-

q0 <= in1;

-

q1 <= q0;

-

q2 <= q1;

-

end

-

-

end

-

-

assign in1 = !q0 & !q1;

-

assign out2 = q2;

-

-

-

-

endmodule

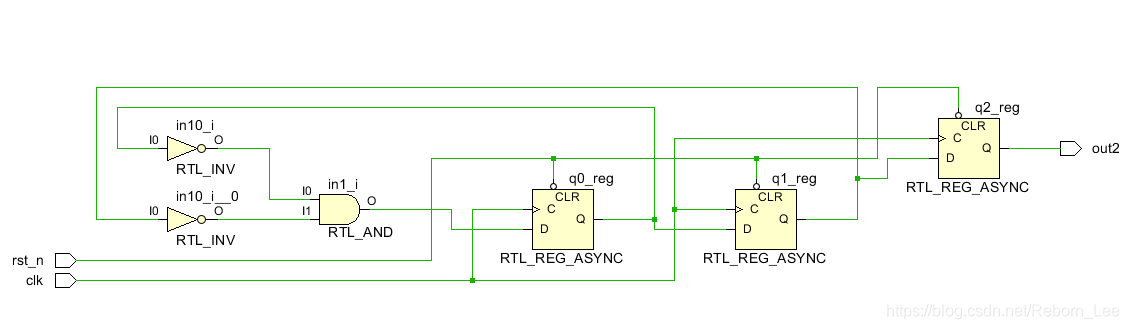

生成对应的RTL原理图:

可见,和题目所给的电路图几乎一致。

在仿真验证:

-

`timescale 1ns / 1ps

-

//

-

// Company:

-

// Engineer: reborn lee

-

//

-

// Create Date: 2019/07/24 20:19:38

-

// Design Name:

-

// Module Name: sim_test

-

//

-

-

-

module sim_test(

-

-

);

-

reg clk;

-

reg rst_n;

-

-

wire out2;

-

-

initial begin

-

clk = 0;

-

forever

-

#2 clk = ~clk;

-

-

end

-

-

-

initial begin

-

rst_n = 1'b0;

-

-

#5

-

rst_n = 1'b1;

-

-

end

-

-

-

test test_tb(

-

.rst_n(rst_n),

-

.clk(clk),

-

.out2(out2)

-

-

);

-

-

-

-

-

endmodule

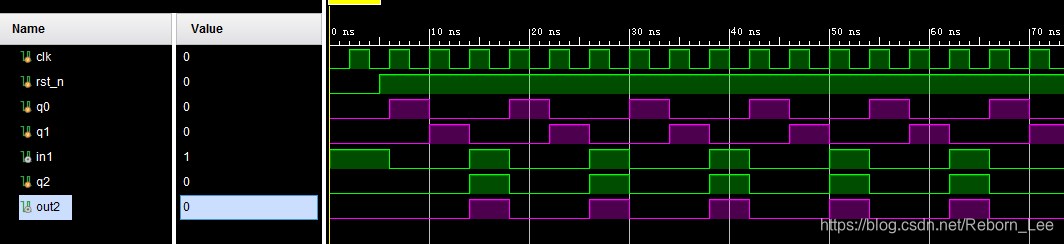

观察波形图,与我们分析的一致。

最后至于这个电路的功能?

这会是什么功能呢?我暂时不敢多说,欢迎评论,给出你的答案。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/97177293

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)