谈谈周期约束

我们常常会看到IC/FPGA的笔试题中经常会让求最小时钟周期或者最高时钟频率问题,这些也不是没有道理的,它是时序分析的基础,周期约束的根据也是如此。

FPGA系统设计通常分为两种,一种是给定时钟频率,这时系统设计的目标是确保两个触发器之间的延迟不会超过1个时钟周期。我们需要控制逻辑门延迟,使得门延迟不会大于最大门延迟(它会出题让你算最大门延迟)。

另一类是时钟频率不固定,这时我们要尽量降低门延迟,最大程度的提高系统的时钟频率。

在实际的FPGA逻辑设计中,我们通常会有一个固定的时钟,我们设计中的关键路径延迟既不能太大,也不能太小,太大会导致建立时间不满足,太小会导致保持时间不满足。

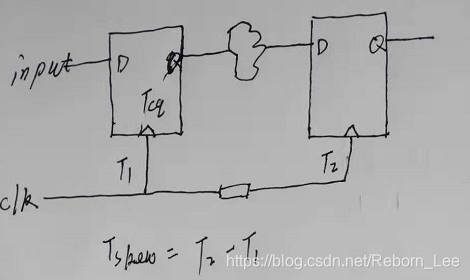

下面给出一个通常的关键路径模型:

最小时钟周期公式为:

Tcycle = Tcq + Tgate + Tsu - Tskew;

这里没有考虑布线延迟,或者把布线延迟包含在了Tgate中了,大家心里明白就好了。

之所以要减去时钟偏斜,会下图可以看出:

如上图是正时钟偏斜,但是推理出来的公式都是一样的,这个时钟偏斜会改善时序,貌似让时钟周期的更大了,这样更有利于建立时间的满足。

我们的延迟时间Tcq+Tgate+Tsu不能大于Tcycle+Tskew,由于Tcq,Tsu一般是固定的,由器件决定,所以就要求我们的门延迟,不能太大,太大则会导致建立时间不满足,也就是时序违规。

但是如果门延迟太小了呢?

我们看看保持时间应该满足什么条件:

如上图:

Thold+Tskew < Tcq + Tgate;

Tskew如果是正的,也就是正时钟偏斜,会不利于这个公式的实现;

Thold,Tskew,Tcq,一般是固定的,所以 能不能满足这个公式就取决于Tgate,门延迟太小,会导致这个公式不满足,也就是时序违规。

所以,门延迟不能太大,也不能太小。

说了这么多,说了好似不太相关,但其实不然,我都是为了周期约束准备的。

我们的时序分析工具(Vivado中集成)要分析时序是否违规,参考是什么呢?

它算出了各种实际的延迟,然后需要报告时序是否违规,当然要和你的要求相比较,这就需要约束。

我们需要告诉时序分析工具的信息很多,但今天这里谈谈最简单的时钟周期约束:

在XDC中,我们使用create_clock 语法:

create_clock -name clk -period 10 [get_ports sysclk],这句xdc命令告诉编译器,时钟clk,从sysclk(get ports 后面摄取的是顶层要分配引脚的物理引脚,get pins后面摄取的是生成的某个寄存器或者器件的引脚,get nets摄取的是里面生成的某根线)这个引脚输入,时钟周期是10ns,由于相位和占空比未声明,所以初相位为0,占空比为50%。如下图:

如果想调节初相位90°和占空比25%:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports sysclk]

这里-waveform {2.5 5}代表第一个跳变沿在第2.5ns处产生,第二个跳变沿在5ns处产生从而形成下图的时钟,这样就可以把所有的相位和占空比关系都描述清除。

编译器会根据时钟sysclk的周期和相位,在整个sysclk时钟域,计算延迟后对比sysclk和对应寄存器的数据端口进行对比,看是否满会产生竞争冒险,不满足的地方会报告出来。

最后一段语法参考:https://mp.weixin.qq.com/s/3WoAO4aHYTqTWLTnF56zMA?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/98733404

- 点赞

- 收藏

- 关注作者

评论(0)