Verilog 中如何无误使用 generate for?

用一个例子开题:

Given an 8-bit input vector [7:0], reverse its bit ordering.

即完成输入输出位的反转。

当然我们可以直接进行8条assign out[1] = in[7];....;

但是如果是更多条如此的重复性赋值呢?我们自然知道要使用for语句,但是如何标准的使用呢?

下面介绍generate来完成这个工作。

生成语句可以动态的生成verilog代码,当对矢量中的多个位进行重复操作时,或者当进行多个模块的实例引用的重复操作时,或者根据参数的定义来确定程序中是否应该包含某段Verilog代码的时候,使用生成语句能大大简化程序的编写过程。

生成语句生成的实例范围,关键字generate-endgenerate用来指定该范围。生成实例可以是以下的一个或多个类型:

(1)模块;(2)用户定义原语;(3)门级语句;(4)连续赋值语句;(5)initial和always块。

generate语句有generate-for,generate-if,generate-case三种语句。

这里重点介绍generate for语句。

先给出标准写法:

-

module top_module(

-

input [7:0] in,

-

output [7:0] out

-

);

-

genvar i;

-

generate

-

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

-

assign out[i] = in[7 - i];

-

end

-

-

endgenerate

-

-

endmodule

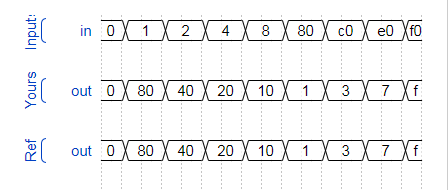

效果:

好了,大概怎么写应该知道了吧,那么需要注意什么呢?

(1) 必须有genvar关键字定义for语句的变量。

(2)for语句的内容必须加begin和end(即使就一句)。

(3)for语句必须有个名字。

上面的代码可以用下面的代码代替:

-

module top_module(

-

input [7:0] in,

-

output [7:0] out

-

);

-

reg out;

-

genvar i;

-

generate

-

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

-

always@(*) begin

-

out[i] = in[7 - i];

-

end

-

end

-

-

endgenerate

-

-

endmodule

最后指出一种,虽然没有使用generate,但是还可以为重复性的赋值提供便利:

-

module ex(

-

-

);

-

-

-

always@() begin: block_name

-

integer i;

-

if() begin

-

for(i = 0; i < N; i = i + 1) begin

-

......;

-

end

-

end

-

else begin

-

......;

-

end

-

-

end

-

-

-

endmodule

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/99567453

- 点赞

- 收藏

- 关注作者

评论(0)