IC/FPGA笔试题分析(六)用16bit加法器IP核实现8bit乘法运算(文末彩蛋)

本来突发奇想,想建立一个群来召集各路同行加入,共同讨论数字IC以及FPGA方向的笔试,面试题目,效果比想象中的要好,大家气氛很好,踊跃发言,大胆讨论,解决了很多有意思的问题,这里挑出两个题目来记录一下,个人感觉写的很好:

题目是:

本身快被遗忘了的一个题目,被大家的讨论掩盖过去了,可是好题终究还是会被发现,这位大哥就单独告诉我并给出了自己的思路,十分感谢,领教了。

-

module mul8bits(

-

input clk,

-

input rst_n,

-

-

input [7:0] a,

-

input [7:0] b,

-

-

output reg [15:0] result

-

-

);

-

-

reg [15:0] areg;

-

reg [15:0] temp;

-

reg [3:0] cnt;

-

-

always@(posedge clk or negedge rst_n)begin

-

if(~rst_n) begin

-

areg <= {8{1'b0}, a};

-

temp <= 16'd0;

-

cnt <= 4'd0;

-

result <= 16'd0;

-

end

-

else if(cnt <= 7) begin

-

cnt <= cnt + 1;

-

areg <= areg <<1;

-

if(b[cnt]) begin

-

temp <= temp + areg;

-

else temp <= temp;

-

end

-

end

-

else begin

-

cnt <= cnt;

-

areg <= {8{1'b0},a};

-

result <= temp;

-

end

-

end

-

-

-

endmodule

上面的Verilog设计中,没有用到IP核,加入有一个IP核的例化模板为:

-

add16 inst_add16(

-

.in1(), //16bit

-

.in2(), //16bit

-

.sout(), //16bit

-

.cout() //1bit进位

-

-

);

当然还必须要求这个IP核必须在一个时钟内完成,是一个组合逻辑,且组合逻辑延迟不能大于一个时钟周期。

那么我们可以更改设计为:

-

module mul8bits(

-

input clk,

-

input rst_n,

-

-

input [7:0] a,

-

input [7:0] b,

-

-

output reg [15:0] result

-

-

);

-

-

reg [15:0] areg;

-

reg [15:0] temp;

-

reg [3:0] cnt;

-

-

always@(posedge clk or negedge rst_n)begin

-

if(~rst_n) begin

-

areg <= {8{1'b0}, a};

-

temp <= 16'd0;

-

cnt <= 4'd0;

-

result <= 16'd0;

-

end

-

else if(cnt <= 7) begin

-

cnt <= cnt + 1;

-

areg <= areg <<1;

-

if(b[cnt]) temp <= temp_w; //调用IP核

-

else temp <= temp;

-

end

-

else begin

-

cnt <= cnt;

-

areg <= {8{1'b0},a};

-

result <= temp;

-

end

-

end

-

-

wire [15:0] temp_w;

-

-

add16 inst_add16(

-

-

.in1(temp),

-

.in2(areg),

-

.sout(temp_w),

-

.cout()

-

-

);

-

-

-

endmodule

本想,自己写一个超前进位加法器来代替这个IP核的,后面再写吧,很晚了。

https://blog.csdn.net/Reborn_Lee/article/details/99634895

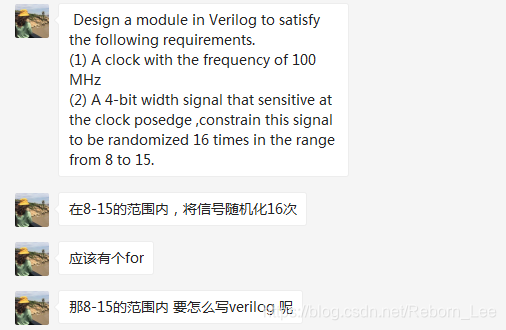

再给出一个仿真相关的题目:

题目翻译过来就是:

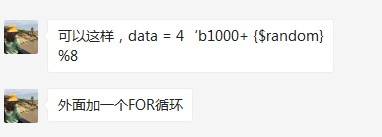

在Verilog中设计模块以满足以下要求。

(1)频率为100MHz的时钟

(2)对时钟敏感的4位宽信号,限制该信号在8到15的范围内随机化16次。

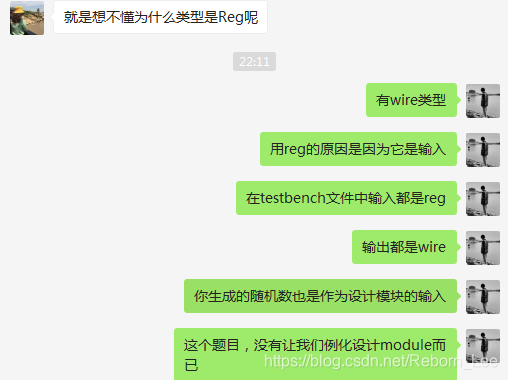

之后也是提问者自己给出的答案,真是提问能激发人的思考呀:

我给出完整代码:

-

`timescale 1ns/1ps

-

module random1();

-

reg clk;

-

reg [3:0] out_rand;

-

-

initial begin

-

clk = 0;

-

forever

-

#5 clk = ~clk;

-

end

-

-

//always begin

-

// #5 clk = ~clk;

-

//end

-

-

-

-

integer i;

-

-

initial begin

-

-

for(i = 0;i < 16; i = i + 1) begin

-

@(posedge clk) begin

-

out_rand = 4'b1000+ {$random}%8;

-

end

-

end

-

-

end

-

endmodule

OK,谢谢各位。

最后还是要邀请更多的同行加入这个IC前端/FPGA笔试面试交流群,加我微信,拉你进群:ljs521615

见链接:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/99998952

- 点赞

- 收藏

- 关注作者

评论(0)