Verilog中关于for与generate for用法和区别的一点愚见

这里不对二者进行全面的举例分析,因为水平有限,只是对这两者之间的区别有些疑惑,是不是for能用的地方,generate for也能用呢?又如何用呢?

关于generate for的总结见博文:Verilog 中如何无误使用 generate for?

还是举这个例子:

https://hdlbits.01xz.net/wiki/Vectorr

Given an 8-bit input vector [7:0], reverse its bit ordering.

即实现输出与输入之间的反转,这是一件重复性的工作,很容易想到用generate for结构,写法如下:(注意for要有名字)

-

module top_module(

-

input [7:0] in,

-

output [7:0] out

-

);

-

genvar i;

-

generate

-

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

-

assign out[i] = in[7 - i];

-

end

-

-

endgenerate

-

-

endmodule

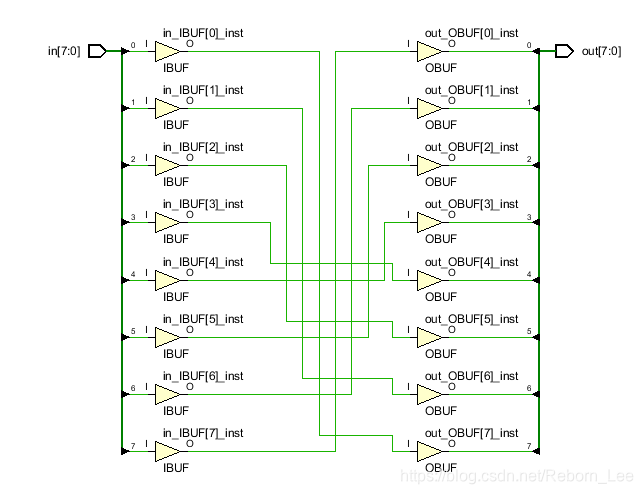

综合后的原理图:

当然,也能用for来实现,只是写法略有不同,注意for不能单独使用,要放到always块内使用,且always块要有名字:

-

module top_module(

-

input [7:0] in,

-

output [7:0] out

-

);

-

reg [7:0] out;

-

always@(*) begin: bit_reverse

-

integer i;

-

for(i = 0;i <8; i = i + 1) begin

-

out[i] = in[7-i];

-

end

-

end

-

-

endmodule

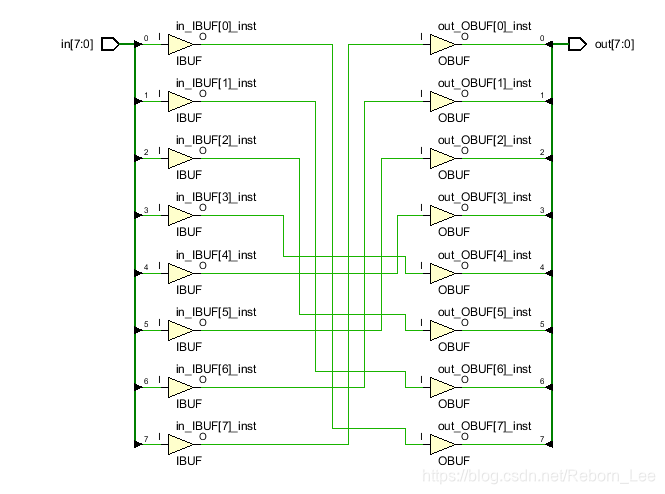

综合后的原理图:

可见,针对这个例子,二者综合出来的电路没有任何区别,都能使用,只是写法不同,需要注意的要点也不同。

在实验一个例子,采用时序逻辑,能说明问题即可:

-

module top_module(

-

input sysclk,

-

input [3:0] a,

-

output [3:0] temp

-

);

-

reg [3:0] temp = 0;

-

genvar i;

-

generate

-

for (i = 0; i < 4 ; i = i + 1) begin: timing_logic

-

always @(posedge sysclk) begin

-

temp[i] <= a[i];

-

end

-

end

-

endgenerate

-

-

endmodule

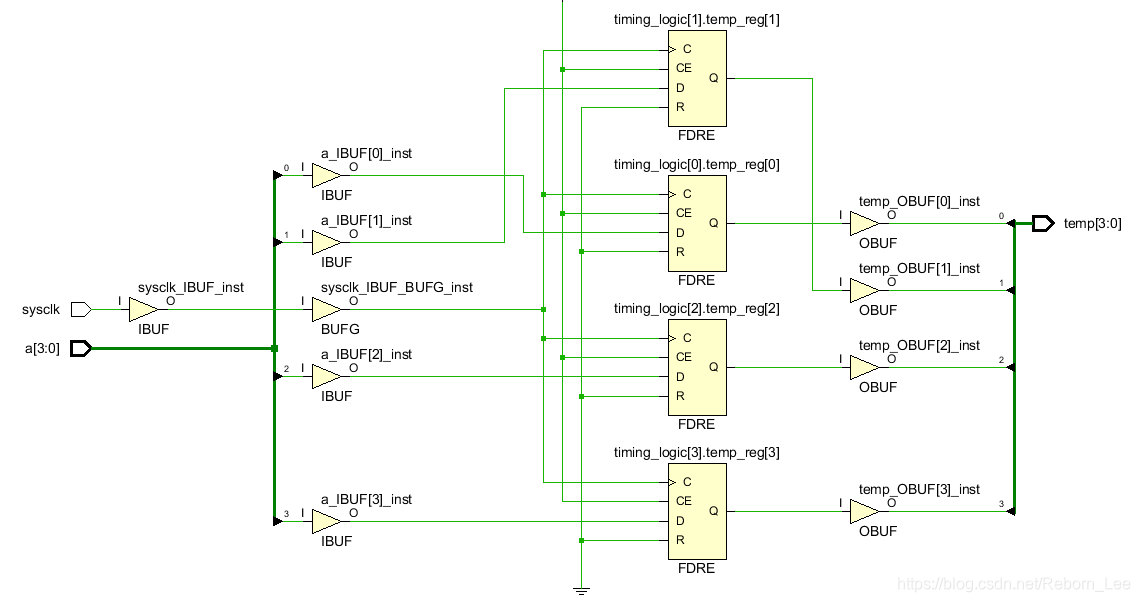

和我们想象的一样,用了四个触发器来延迟一拍。

下面用for来实现:

-

module top_module(

-

input sysclk,

-

input [3:0] a,

-

output [3:0] temp

-

);

-

reg [3:0] temp = 0;

-

-

-

-

always @(posedge sysclk) begin: timing_logic

-

integer i;

-

for (i = 0; i < 4 ; i = i + 1) begin

-

temp[i] <= a[i];

-

end

-

end

-

-

-

endmodule

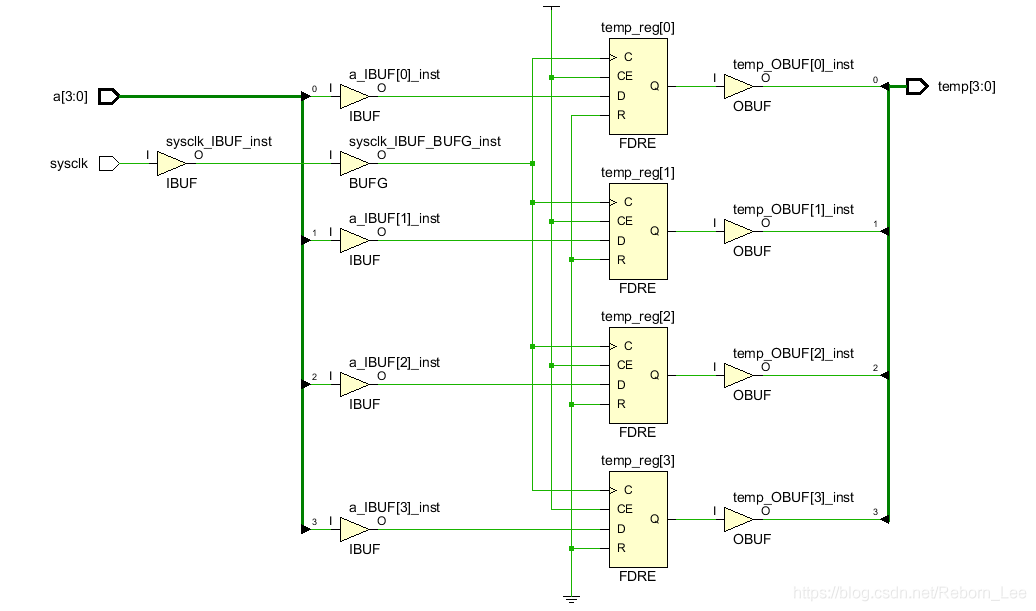

你能看出区别吗?

至少这两个例子,综合出来的电路完全没有区别,只是语法上的区别而已。

到这里,还不能给出结论,因为这只是凤毛麟角,两个最容易想到的例子而已。

各位如何看待,二者的区别在哪里?欢迎给出评论。

最后说下:

一年一度的校招又来了一段时间了,突然发现,一个人的力量是有限的,面对很多笔试,面试中的很多问题,也许会感到很无助,于是决定建立一个群,专门用来分享,讨论笔试面试题目。

群二维码见链接:https://blog.csdn.net/Reborn_Lee/article/details/99715080

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/99738300

- 点赞

- 收藏

- 关注作者

评论(0)