IC/FPGA笔试/面试题分析(七)建立时间和保持时间类型考题汇总分析

自从召集2020届校招同行加入新建立的“IC/FPGA校招笔试面试交流群“,见识到了很多关于建立时间和保持时间分析的题目,在为别人解答疑惑,以及别人为自己解答疑惑的同时,自己对于知识的理解更加深刻了。

对于建立时间而言,从单独的对触发器的建立时间和保持时间的分析到了对电路(系统)的建立时间到保持时间的分析,前者是核心,后者是扩展,后者建立在前者的基础之上进行推到得到,同时也是芯片内部实际遵循的时序规则。

注:下面博文中的蓝色字体均为链接!

以下图片均来自互联网以及群内讨论。

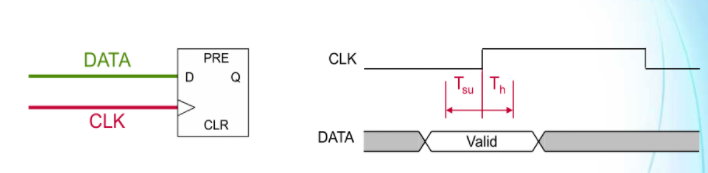

对于触发器的建立时间和保持时间,可见之前的博文:

从这篇博文上,我们可以知道建立时间和保持时间的概念,建立时间就是时钟有效沿到来之前数据必须保持稳定的时间,而保持时间就是时钟有效沿到来之后数据必须保持稳定的时间,如果不满足建立时间或保持时间,就会导致时序违规,这对电路的功能实现是有很大影响的。

我们还可以了解到Tco这个时序参数,它的名字是数据输出延时,它是对于触发器而言的,含义是从触发器的时钟有效开始,数据从输入到输出之间的延迟。(触发器的数据输入到输出是有一段时间的,所以有这么一个说法,采样反应更快的触发器可以改善时序)

从博文: 谈谈周期约束中可以知道时钟偏斜对于建立时间和保持时间的影响,例如正时钟偏斜对于建立时间的满足是有帮助的,而对保持时间的满足是有害的。

我们还可以得知,对于组合逻辑的延迟,也即触发器之间的门延迟,不能太大,也不能太小,太大会导致(关键路径)建立时间不满足,太小会导致(关键路径)保持时间不满足。

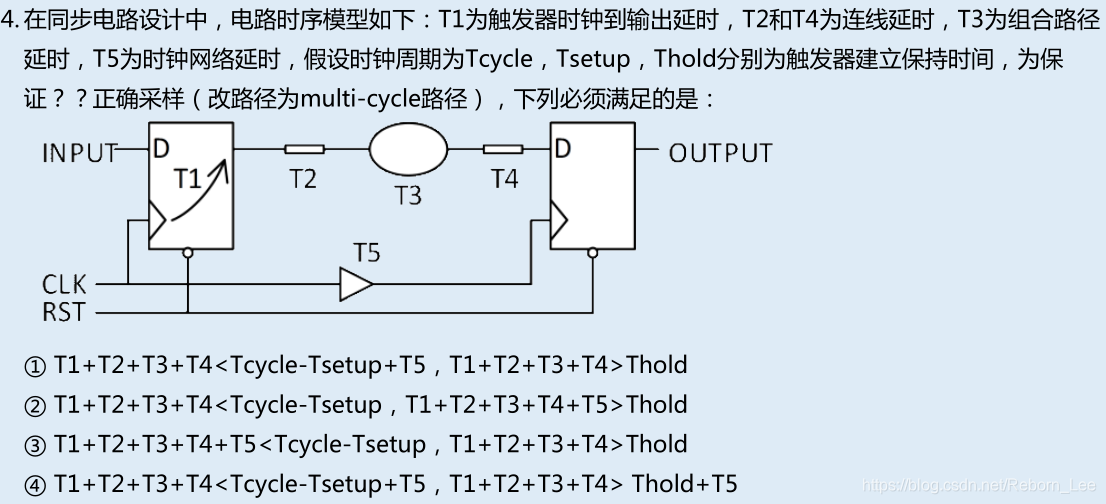

例题一:

有了这些基础,我们从最简单的考题分析:IC/FPGA笔试题分析(五)

这个题目堪称经典中的经典,因为从这个题目是标准的建立时间和保持时间考题,并从中可以总结出系统最大时钟频率以及建立时间和保持时间需要满足的公式。

我们知道系统周期需要满足的条件是:

Tcycle + Tskew > Tco + Tgate + Tsu;

代入上面的条件,得知

Tcycle + T5 > T1 + T2 + T3 + T4 + Tsetup

上面的时钟路径是存在偏斜的,而且是正时钟偏斜,则对于保持时间的满足更加的困难,需要满足:

Thold + Tskew < Tc0 + Tgate

代入上面的条件,得: Thold + T5 < T1 + T2 + T3 + T4

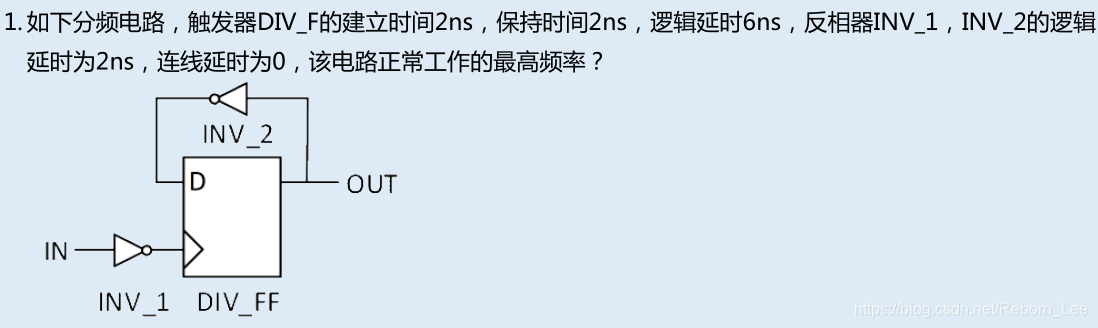

例题二:

在上题的基础上,你也许会分析触发器的建立时间和保持时间应该满足的关系了,可是考题也许会变了法的考你,如下:

求系统的最高频率?

就一个触发器,我怎么办呢?

仔细看来,这是一个触发器到自身的反馈,可以看做两个触发器之间进行数据传输,其实也就是如此。

需要明白的是,由于时钟到达这个触发器的时间一致,所以不存在时钟偏斜。

给出系统周期满足的关系:

Tcycle > Tco + Tgate + Tsu = 6 + 2 + 2= 10ns

所以时钟最大频率可以为100MHz。

例题三:

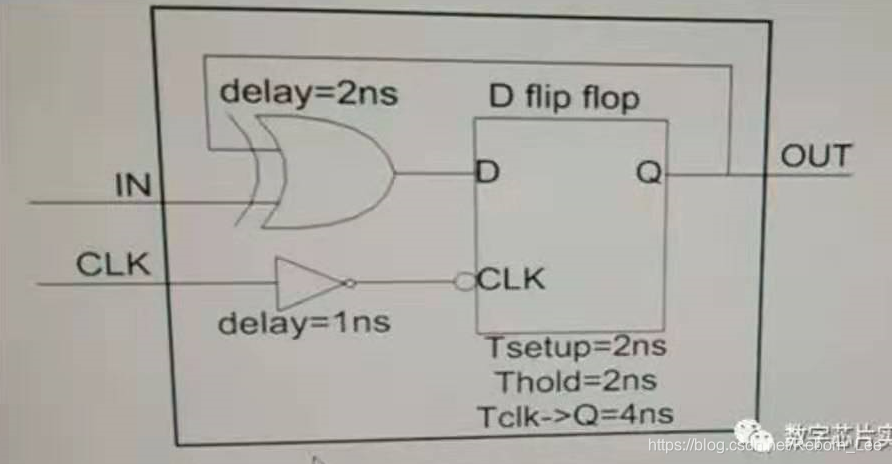

如果都是分析触发器的建立时间和保持时间就好了,可惜不是这样的,套路来了:

如下图,将框内的电路作为一个寄存器,那么其有效的建立时间和保持时间是多少?

这个题目猛地一看就让人懵逼了,我还曾因项目调试不顺利,遇到这个题目,心态炸裂过。。。(年轻)

求框内电路的有效建立时间和保持时间,给出了框内触发器的建立时间和保持时间以及其他一些逻辑的延迟,我们就以触发器的建立时间和保持时间为准来倒逼整个电路的建立时间和保持时间,一切还都是为了让触发器满足时序要求。

有效建立时间分析:

假设电路的有效Setup为Tsetup_valid:

对于D触发器而言,其本身的建立时间是2ns,也就是说数据必须在时钟有效沿到达之前2ns保持稳定,这样到达D端后就一定是稳定的数据了。

这个电路的数据来自于IN,时钟来自于CLK;

考虑时钟路径延迟影响:

时钟CLK要早于触发器的时钟1ns到达,因此对于D触发器建立时间的满足是有害的,电路有效建立时间

Tsetup_valid = Tsetup - 1ns = 1ns(因为数据需要提前1ns稳定下来)

考虑数据路径延迟影响:

Tsetup_valid = Tsetup - 1ns + 2ns = 3ns;(经过组合逻辑后的数据需要在时钟有效沿之前Tsetup时间稳定下来)

有效保持时间分析:

和建立时间分析套路一致,对于D触发器而言,数据需要在时钟有效沿到来之后保持Thold时间。

考虑时钟延迟的影响:

考虑到电路时钟对于触发器时钟早到1ns,所以电路有效保持时间Thold_valid = Thold + 1ns = 3ns;

考虑路径延迟影响:

数据需要经过一段组合逻辑之后才能保持稳定,因此电路的有效保持时间为:

Thold_valid = Thold + 1ns - 2ns = 1ns。

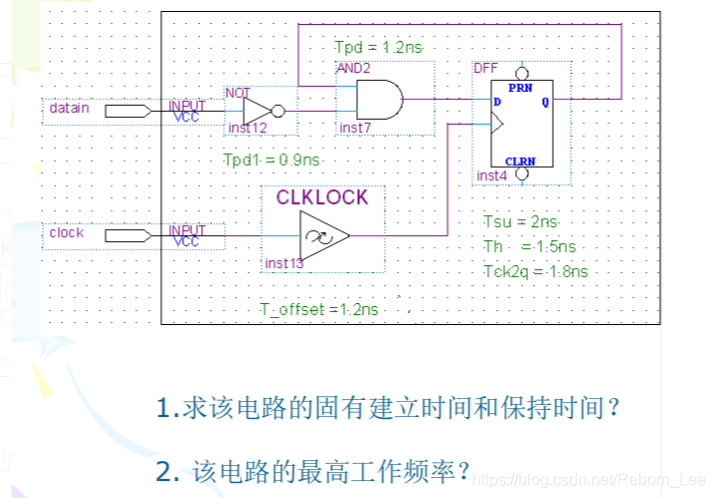

例题四:

下面这个题目和上面题目相差无几:

求电路的固有建立时间和保持时间和上一题的有效建立时间和保持时间是一个意思的。

因此固有建立时间为Tsu_valid = Tsu - T_offset + Tpd + Tpd1 = 2 - 1.2 + 1.2 + 0.9 = 2.9ns

固有保持时间为:Th_valid = Th + T_offset - Tpd - Tpd1 = 1.5 + 1.2 - 1.2 - 0.9 = 0.6ns.

而系统的最高频率呢?

先求系统的最小周期,考虑两个触发器之间的路径:

Tmin = Tco + Tpd + Tsu = 1.8 + 1.2 + 2 = 5ns,那么系统最高频率为200MHz。

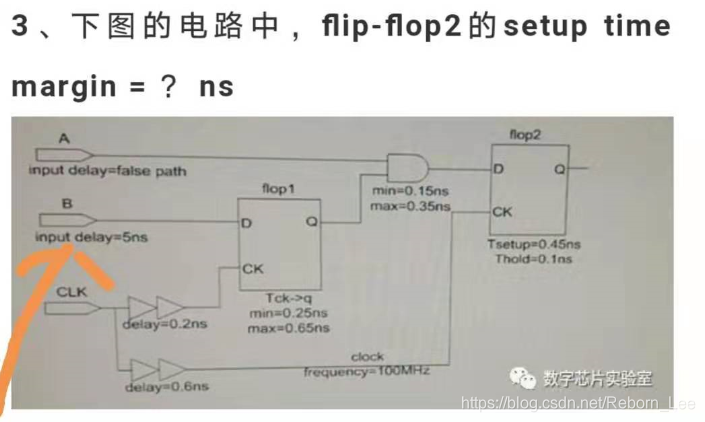

例题五:

这个题目让求setup time margin,意思大概就是建立时间裕量,就是系统周期减去Tco,Tgate以及Tsu之后还可以有多少裕量,那,Tco,Tgate以及Tsu当然要用最大的来代入,因为要保证系统在最恶劣的情况下,能有多少裕量。

因此:

Tmargin = 10ns + 0.6ns - 0.2ns - 0.65ns - 0.35ns - 0.45ns = 8.95ns

其中0.6ns - 0.2ns表示的是时钟偏斜量,可见是时钟整偏斜,有利于时钟裕量。

总结开来,最难的部分应该是求电路的固有建立时间和保持时间了吧,建立时间和保持时间是一对冤家,利你不利它,如果你分析了建立时间,那么保持时间相反就可以了,例如逻辑门延迟不利于系统建立时间(+),那么不利于系统保持时间(-),时钟延迟有利于系统建立时间(-),则不利于系统保持时间(+)。

可以当做偏方服用。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/100049997

- 点赞

- 收藏

- 关注作者

评论(0)