再谈BUFFER

又复习了一遍博客:【FPGA】FPGA中的缓冲与驱动那些事

感觉还是有必要根据自己的理解来写一篇有管buffer的博客的。

例如FPGA的时钟有外部晶振提供,我内部处理需要多个频率的时钟,这时候也许需要使用多个分频器(PLL,或MMCM等),外部晶振进来的时钟不能驱动多个PLL(两个都不能),我们需要使用IBUFG或IBUFGDS原语,外部时钟是单端的就用IBUFG,如果是差分的,就用IBUFGDS之后在驱动各个PLL,(也就是作为PLL的输入),就没有问题。

上面所说的也就是一个时钟上树问题,上全局时钟树,让输入时钟信号变得驱动能力强,产生的时钟偏斜小,抖动小。IBUFG,IBUFGDS

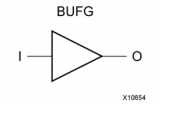

BUFG

BUFG叫 Global Clock Simple Buffer,自然和时钟有关,它的作用是使经过这个Buffer的信号能够具有高扇出,驱动能力强的能力,使信号接入全局布线资源,使得信号具有低偏斜的特性;既然是一个时钟buffer,当然时钟信号首当其冲,但不仅仅局限于此,还可以是复位,置位以及时钟使能等需要具有高扇出的信号。

但这个buffer需要组合使用,不需要你在Verilog设计中去例化。

一般情况下IBUFGDS+BUFG或者IBUFG+BUFG可配套使用,当全局时钟扇出较少的时候可以不加BUFG。

一般FPGA的输入时钟(一般来自晶振)先经过IBUFGDS,IBUFGDS需要自己例化,例如:

-

IBUFG #(

-

.IBUF_LOW_PWR("TRUE"), // Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

-

.IOSTANDARD("LVCMOS18") // Specify the input I/O standard

-

) IBUFG_inst (

-

.O(fpga_clk), // Clock buffer output

-

.I(fpga_clk1) // Clock buffer input (connect directly to top-level port)

-

);

之后的BUFG可以根据综合工具进行推断。

上面都是讲的时钟信号,那非时钟信号呢?有时候也会有一些需求,例如AD采样出来的数据是差分数据,我需要转换为单端信号在FPGA内部进行数据处理,我就需要差分转单端的Buffer,例如:

-

generate

-

genvar j;

-

for(j=0;j<10;j=j+1): ibufds10

-

begin

-

IBUFDS ibufds_inst1

-

(

-

.I(ad1_bp[j]),

-

.IB(ad1_bn[j]),

-

.O(ad_data_b[j])

-

);

-

end

-

endgenerate

这里还牵扯到了generate for的使用:generate for

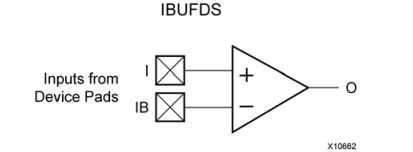

IBUFDS

IBUFDS叫做Differential Signaling Input Buffer,顾名思义,是一个差分输入的buffer,差分信号转单端信号。

输出取决于主输入I;

需要在RTL设计中用例化的方式来使用。

最后说一句,这个原语是针对信号的,能够改善信号完整性,使用这个原语的原因在于差分信号在片内不经过这个原语不能直接处理。

我们平时使用的selectIO IP核的信号输入也可以是差分的,其实内部也用到了这些原语,这个黑盒子谁知道呢?

这些东西在Vivado的原语模板里都能找到,就不在贴出例化模板了。

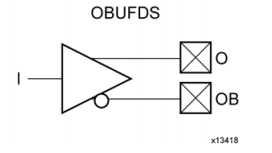

OBUFDS

OBUFDS叫做Differential Signaling Output Buffer,也即单端转差分的一个buffer,针对差分信号的一个buffer。

使用方法也是通过在RTL代码设计中例化使用。

写在最后,我们看数据手册时候,还会看到IBUFDS以及OBUFDS有这样一段描述,支持低压差分信号等等,他的意思就是:IBUFDS、IBUFGDS和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。

输入是差分信号电平可能是LVDS,输出是单端信号,电平是LVCOMS18等

参考自数据手册:Vivado Design Suite 7 Series FPGA and Zynq-7000 SoC Libraries Guide (UG953)

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/100173119

- 点赞

- 收藏

- 关注作者

评论(0)