IC/FPGA笔试/面试题分析(十)CMOS门电路

目录

CMOS介绍

MOS管分为NMOS和CMOS,二者成对出现在电路中,且二者在工作中互补,构成CMOS管;

MOS管有增强型和耗尽型,数字电路中,多采用增强型MOS管。

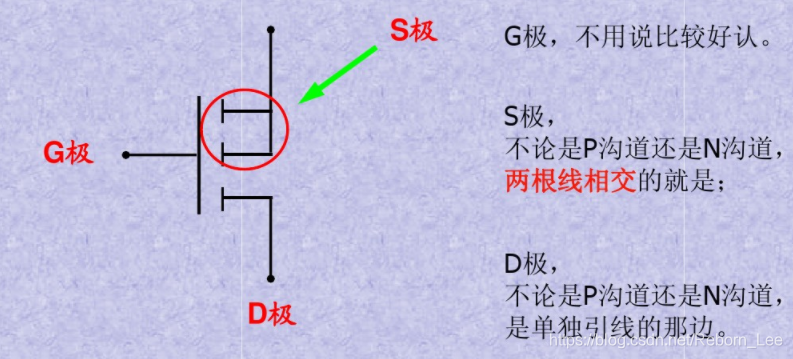

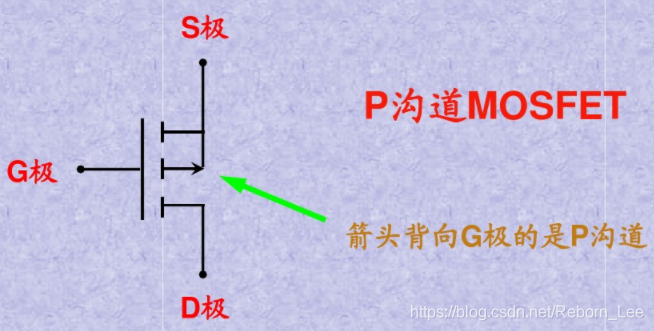

如何识别MOS管的三个极,例如G(栅极),D(漏极),S(源极):(MOS管原理)?

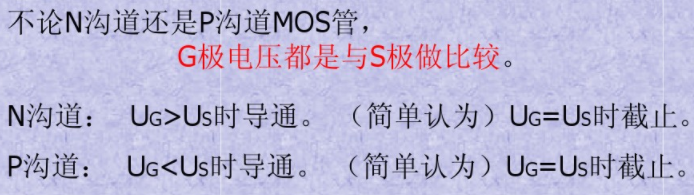

MOS管何时导通?

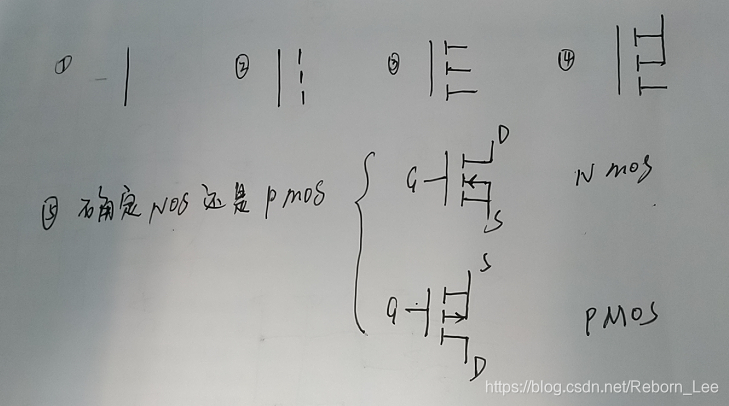

如何画一个PNOS或一个NMOS?

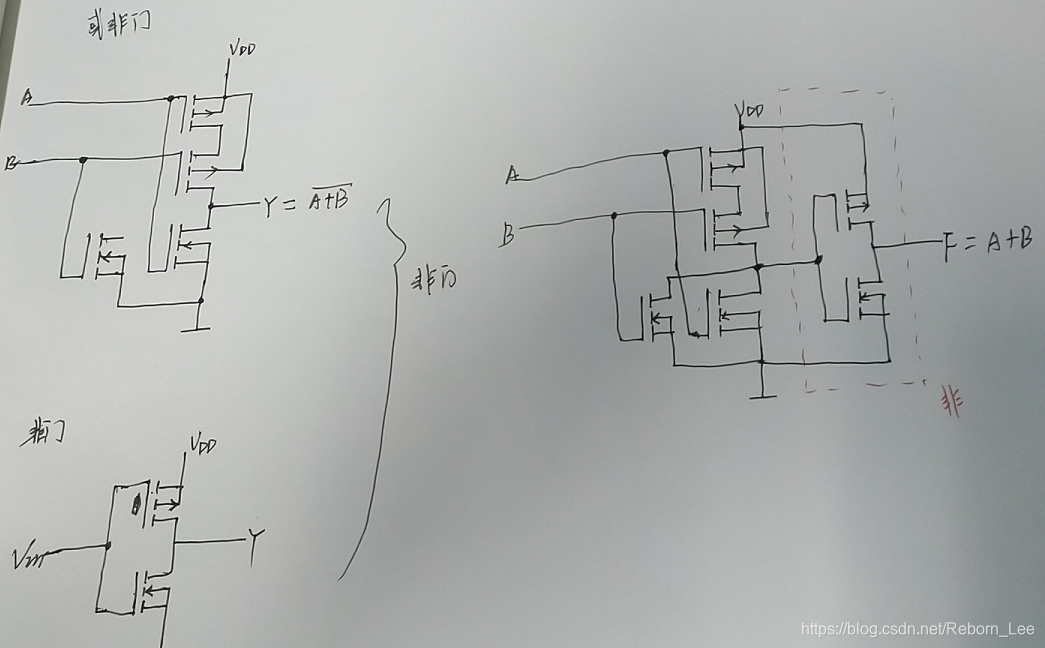

CMOS非门

第一个CMOS门电路:

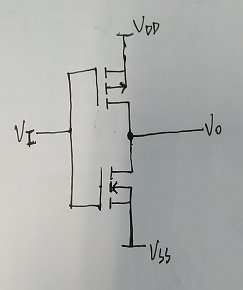

CMOS反相器:

如何构成一个反相器的呢?

从上图可以看出,下面是一个NMOS,上面是一个PMOS,当输入VI为低电平(0)时,由于Vgs1为0,下方NMOS不导通(内阻很高,相当于断路),而对于上方PMOS,Vgs2 = - Vdd,导通了(相当于短路),所以输出为高电平,相当于对输入取反了。

同理,当VI为高电平(Vdd),则由于下方NMOS的Vgs1为Vdd,所以导通,而上方PMOS,由于Vgs2 = 0,所以截止,固输出为低电平0.

综上:无论Vi为高电平还是低电平,NMOS和PMOS总是工作在一个截止一个导通,即互补状态,所以把这种电路结构形式成为CMOS。

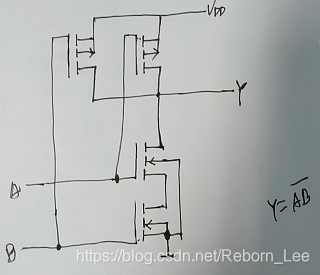

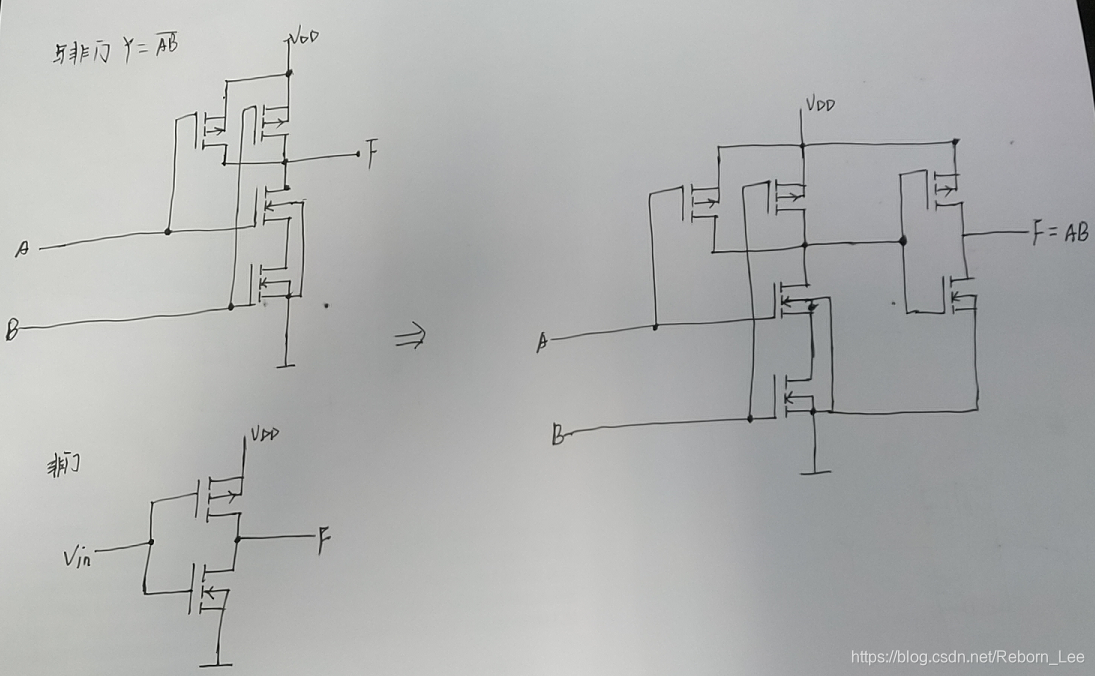

CMOS与非门

上方为PMOS,采用并联连接;

下方为NMOS,采用串联链接;

对于上方PMOS,A和B任一个为低,会导通;对于下部NMOS,A和B任一个为低,都会截止,因此输出为高电平;

如果A和B都为高电平,则上方PMOS截止,下方NMOS都导通,则输出相当于接地,因此输出为低电平。

综上,完成了与非门的作用。

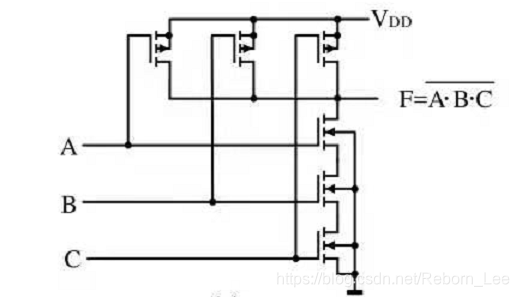

两输入的与非门可以画了,三输入的与非门自然不在话下:

上并下串结构:

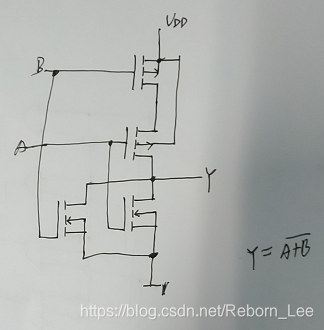

CMOS或非门

如果与非门记忆为上并下串,则这个或非门则为上串下并,且上方均为PMOS,下方均为NMOS;

如果A和B均为0,则下方截止,上方两个PMOS均导通,则输出为高电平;

只要A和B有一个为高电平,则上方PMOS截止有一个截止,下方NMOS有一个导通,由于NMOS为并联,所以输出Y为低电平。

综上所述,为一个或非门。

CMOS或门

我们知道了CMOS或非门比较简单,就是上串下并,而且非门的CMOS电路也知道了上PMOS下NMOS的串联,那么或门自然不在话下了。

CMOS与门

同理,与门是一个与非门加一个非门得到,如下:

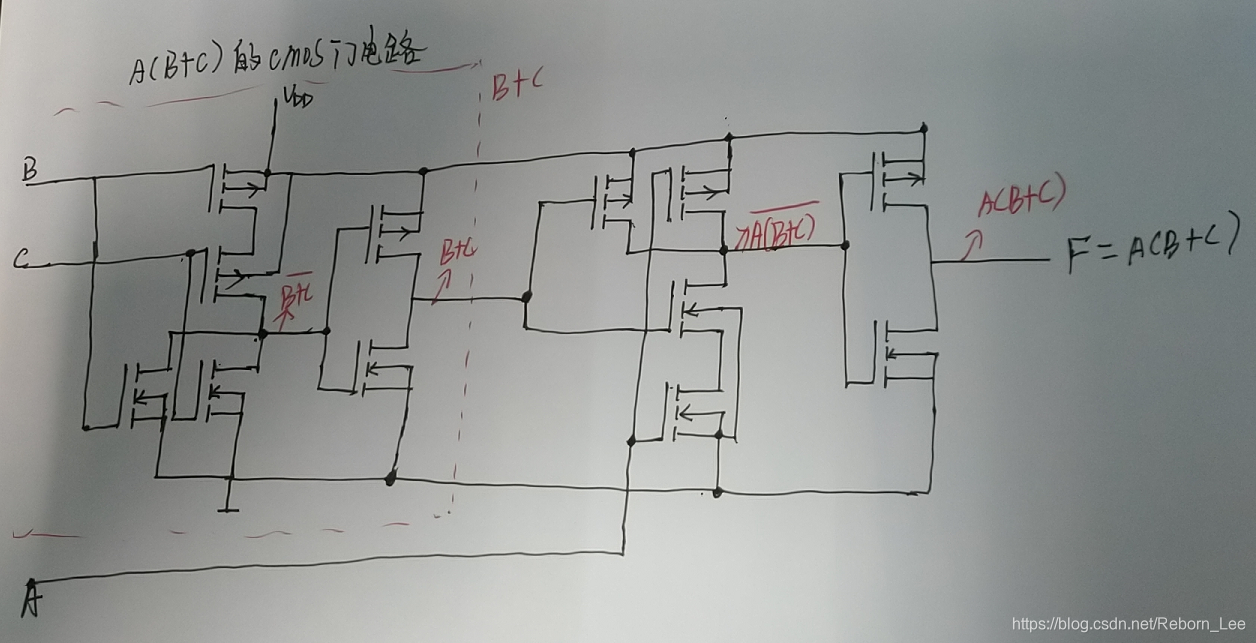

CMOS与或式

用CMOS门画出门电路A(B+C)

这就比上面一些更加复杂了一点,我们上面画的或门,与门以及非门都是为各种组合打基础的。

更确切的说:

最基础的为非门(上P下N),与非(上并下串),或非门(上串下并),

之后由与非和非门结合获得与门;或非与非结合获得或门;

之后或门和与门结合获得与或门;

下面的画法也是这种思路。

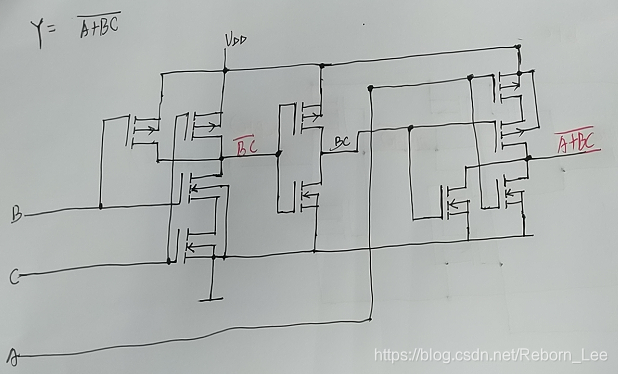

CMOS或与非

同上,不在话下。

最后给出一些参考资料,供查阅:CMOS门电路

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/100659089

- 点赞

- 收藏

- 关注作者

评论(0)