建立时间裕量与保持时间裕量的简单理解

之前刚接触FPGA时候,了解到时序约束这一块,遇到一个概念就是建立时间裕量以及保持时间裕量,让人十分费解;

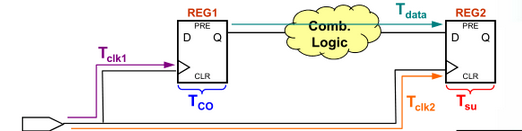

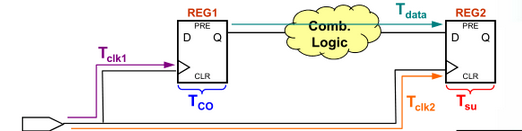

如今秋招已过,也见过许多这种类型的题目,但是大多类似,都是如下模型;

很久以前也有过仔细分析,但是总觉得繁复,让人看了有些恐怖,需要求数据要求时间和数据到达时间,然后建立时间裕量等于数据要求时间减去数据到达时间。如:建立裕量

这样理解也没有问题,可以推出数据的建立裕量:

![]()

上面假设时钟偏斜为零。

当然理解上述推到方法也行,但是我想还是简单粗暴的想法让人更容易理解:

有如下时序模型:

系统时钟需要满足如下关系:

时钟T是固定的,那么建立时间裕量,不过是满足dff建立时钟之后,还宽裕出来的时间:

同理,保持时间需要满足的关系为:

额外提示:

所有的一切Tskew都是如下:

所以,Tskew有可能为正,也有可能为负,负的话就有利于满足保持时间,正的话就有利于满足建立时间;

所以,保持时间裕量也不过是满足dff保持时间后,宽裕出来的时间:

最后,无论是建立时间裕量还是保持时间裕量,为正则满足时序要求,为负则不满足时序。

对于建立时间裕量:

可见,组合逻辑延迟Tgate不能太大,太大会影响建立时间的满足;

对于保持时间裕量:

可见,门延迟Tgate也不能太小,太小则不利于保持时间满足。

回忆参考:时序分析之静态时序分析基础

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/101177036

- 点赞

- 收藏

- 关注作者

评论(0)