有重叠与无重叠序列之序列检测与序列产生

目录

前言

序列检测与序列产生是一对对称的设计,就像有微分就有积分一样。

序列检测分为有重叠检测和无重叠检测;

例如检测序列1101011,我们给出输入:110101101011,如果是无重叠检测,则只能检测到一个序列:1101011_01011;

如果是有重叠检测,则可以检测到两个这样的序列:11010_11_01011。

同理,序列产生也可以分为有重叠序列的产生方法和无重叠序列的产生方法,序列产生的办法也可以用移位寄存器产生,也可以用状态机的方式来产生;这两种方法后面都是提到。

由于序列检测我们之前写的太多了,所以这篇博文的重点不是序列检测而是序列产生。

无重叠序列产生

移位寄存器实现

以产生序列1101011为例,我们产生产生的序列要是这个样子的1101011_1101011..............

所以我们需要使用7位的移位寄存器,每次对序列1101011左移,同时输出最高位;7位的移位寄存器固然需要消耗7个触发器,这也是一个考点。

设计也极其简单,如下:

-

module seq_gen7(

-

input clk,

-

input reset,

-

output out

-

-

);

-

reg [6:0] seq_mid;

-

-

always@(posedge clk or posedge reset) begin

-

if(reset) seq_mid <= 7'b1101011;

-

else seq_mid <= {seq_mid[5:0], seq_mid[6]};

-

end

-

assign out = seq_mid[6];

-

-

endmodule

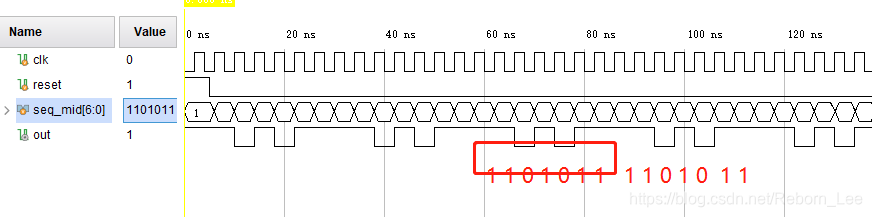

仿真波形:

局部放大:

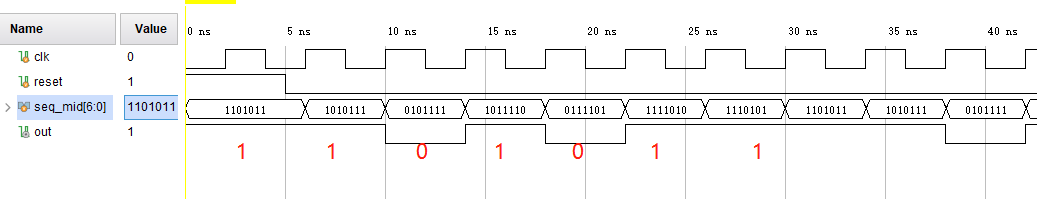

RTL原理图:

可见用了7个触发器。

状态机实现

移位寄存器实现方式,用了7个触发器构成一个7位的移位寄存器来实现上述无重叠序列产生,那如果我们用状态机实现的话, 我们只需要用3个触发器就可以实现,因为我们的状态变量只需要用3位即可,每一个状态产生一个输出,7个状态即可产生这样的一个序列。

设计也很简单,直接用二段式状态机:

-

module seq_gen7(

-

input clk,

-

input reset,

-

output reg out

-

);

-

-

parameter s0 = 3'd0, s1 = 3'd1, s2 = 3'd2, s3 = 3'd3, s4 = 3'd4, s5 = 3'd5, s6 = 3'd6;

-

reg [2:0] cur_state, nxt_state;

-

always@(posedge clk or posedge reset) begin

-

if(reset) cur_state <= s0;

-

else cur_state <= nxt_state;

-

end

-

always@(*) begin

-

nxt_state = s0;

-

case(cur_state)

-

s0: begin

-

nxt_state = s1;

-

out = 1;

-

end

-

s1: begin

-

nxt_state = s2;

-

out = 1;

-

end

-

s2: begin

-

nxt_state = s3;

-

out = 0;

-

end

-

s3: begin

-

nxt_state = s4;

-

out = 1;

-

end

-

s4: begin

-

nxt_state = s5;

-

out = 0;

-

end

-

s5: begin

-

nxt_state = s6;

-

out = 1;

-

end

-

s6: begin

-

nxt_state = s0;

-

out = 1;

-

end

-

default: begin

-

nxt_state = s0;

-

out = 1;

-

end

-

endcase

-

end

-

-

-

endmodule

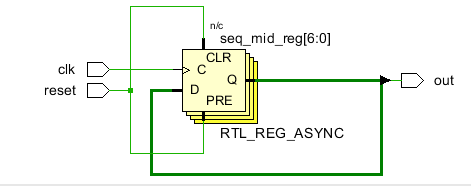

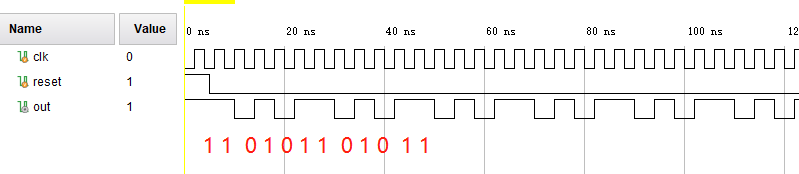

仿真波形如下图:

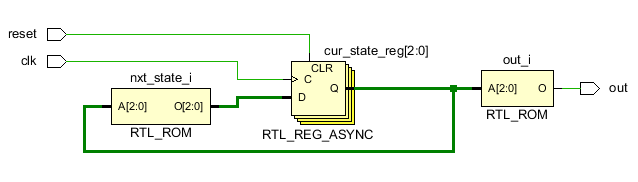

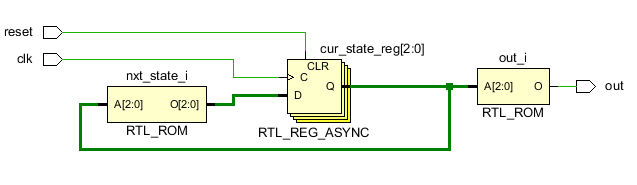

RTL原理图:

可见用了多少个触发器,只需要看时序逻辑部分,也就是状态机的跳转部分,状态变量用了几位就是几个触发器。

有重叠序列产生

移位寄存器方式实现

仍然以产生序列1101011为例,当然这里变成了有重叠序列,也就是产生的序列可以是如下样子:

110101101011...

这个序列中有两个1101011,二者共用11;

因此我们产生这样的序列只需要一个5位的移位寄存器即可:

设计也十分简单,如下:

-

//有重叠序列的移位寄存器实现

-

module seq_gen5(

-

input clk,

-

input reset,

-

output out

-

);

-

reg [4:0] seq_mid;

-

always@(posedge clk or posedge reset) begin

-

if(reset) seq_mid <= 5'b11010;

-

else seq_mid <= {seq_mid[3:0], seq_mid[4]};

-

end

-

assign out = seq_mid[4];

-

-

-

-

endmodule

行为仿真图如下:

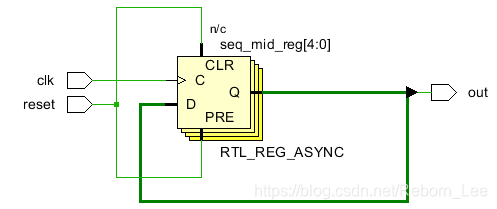

对应的RTL原理图如下:

有了用了5位的移位寄存器,所以需要5个触发器即可实现。

状态机方式实现

设计文件:

-

//有重叠序列的状态机实现

-

module seq_gen5(

-

input clk,

-

input reset,

-

output reg out

-

);

-

-

parameter s0 = 3'd0, s1 = 3'd1, s2 = 3'd2, s3 = 3'd3, s4 = 3'd4;

-

reg [2:0] cur_state, nxt_state;

-

-

always@(posedge clk or posedge reset) begin

-

if(reset) cur_state <= s0;

-

else cur_state <= nxt_state;

-

end

-

always@(*) begin

-

nxt_state = s0;

-

case(cur_state)

-

s0: begin

-

nxt_state = s1;

-

out = 1;

-

end

-

s1: begin

-

nxt_state = s2;

-

out = 1;

-

end

-

s2: begin

-

nxt_state = s3;

-

out = 0;

-

end

-

s3: begin

-

nxt_state = s4;

-

out = 1;

-

end

-

s4: begin

-

nxt_state = s0;

-

out = 0;

-

end

-

default: begin

-

nxt_state = s0;

-

out = 1;

-

end

-

endcase

-

end

-

-

-

-

-

endmodule

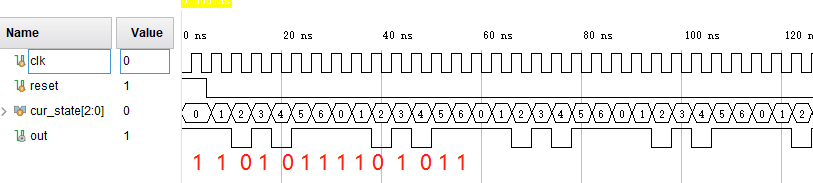

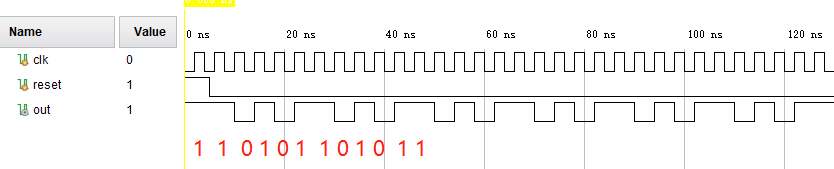

行为仿真图:

RTL原理图如下:

状态变量是3bit的,所以用3个触发器可以实现。

博文推荐

与本博文有关的其他博文列表如下:

序列检测:

IC/FPGA校招笔试题分析(四)再看Moore状态机实现序列检测器

序列产生

最后的最后,如果让产生一个序列,并没有说是有重叠还是无重叠的,问你至少需要多少个触发器实现,那样的话,如果能设计成有重叠的就设计成有重叠的,那样的话就可以节省触发器数量。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/102152072

- 点赞

- 收藏

- 关注作者

评论(0)