【 Sublime Text 】如何使用Sublime Text快速生成代码模板

目录

背景

写的代码多了,会发现几乎每次都要敲那几行代码,例如写三段式状态机,我们只需要改变下内容即可,外壳永远都是一样,有没有方法来快速生成这样的模板呢?

今天看到了这么一个快速生成模板的方法,记录下来,方便以后快速开发。

今天只是使用了sublime,这个软件的好处在于可以生成Verilog模块例化模板,如何做呢?见这篇博客。(准备弃用notepad++)。

实现

工具:Sublime Text

具体操作:首先打开,工具 —— 插件开发 —— 新建代码片段

如果是英文版,则为:Tools > Developer(开发者选项) > new Snippet(新的代码块)

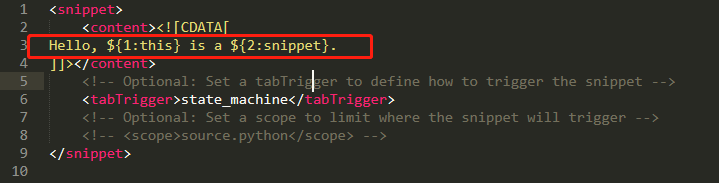

建立一个状态机模板:

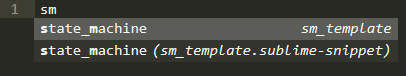

触发命令为state_machine,也就是说,当输入state_machine时候,就会显示模板:

如下图:

tabTrigger 标签中是你的 触发命令,如我触发状态机模板的命令为:state_machine;

之后,在这里写入你的代码模板:

我的三段式状态机模板为:

-

<snippet>

-

<content><![CDATA[

-

-

/*-----third stage state machine start------*/

-

//parameter define

-

parameter s0

-

-

//state variables define

-

reg [N - 1 : 0] cur_state, nxt_state;

-

-

//the first stage

-

always@(posedge clk or negedge rst_n) begin

-

if(~rst_n) cur_state <= 0;

-

else cur_state <= nxt_state;

-

end

-

-

//the second stage

-

always@(*) begin

-

nxt_state = s0;

-

case(cur_state)

-

s0: begin

-

-

end

-

s1: begin

-

-

end

-

-

-

default: begin

-

-

end

-

endcase

-

end

-

-

//the third stage

-

always@(*) begin

-

if() begin

-

-

end

-

else if() begin

-

-

end

-

else begin

-

-

end

-

end

-

-

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>state_machine</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

-

Ctrl + S 保存文件,名称随意,但是文件后缀必须是 .sublime-snippet

这里命令为sm_template.sublime-snippet;

现在测试下效果如何?

先建立一个.v文件,之后输入sm_template,然后Enter或者Tab:

Enter得到如下:

甚为好用,甚为好用呀。

最后给出一个方便的技巧:

就是单独建立一个文件夹,用来存放模板文件。

这样方便重装软件时候,可以直接把此文件夹拷贝到新的安装文件夹中,方便继续使用模板。

Verilog模板

这里给出我定义的其他模板:

计数器:

-

<snippet>

-

<content><![CDATA[

-

-

reg [N-1 : 0] counter;

-

-

always@(posedge clk or negedge rst_n) begin

-

if(~rst_n) counter <= 0;

-

else if()

-

else

-

end

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>counter</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

时序逻辑always块:

-

<snippet>

-

<content><![CDATA[

-

-

always@(posedge clk or negedge rst_n) begin

-

if(~rst_n)

-

else if()

-

else

-

end

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>always_time</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

组合逻辑always块:

-

<snippet>

-

<content><![CDATA[

-

-

always@(*) begin

-

//use if

-

if(~rst_n)

-

else if()

-

else

-

//use case

-

/*

-

case()

-

-

-

endcase

-

*/

-

end

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>always_com</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

低电平复位之异步复位,同步释放电路:

-

<snippet>

-

<content><![CDATA[

-

-

//Asynchronous reset, synchronous release

-

-

reg rstn_r0, rstn_out;

-

-

always@(posedge clk or negedge rst_n) begin

-

if(~rst_n) begin

-

rstn_r0 <= 0;

-

rstn_out <= 0;

-

end

-

else begin

-

rstn_r0 <= 1;

-

rstn_out <= rstn_r0;

-

end

-

end

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>rstn</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

高电平复位之异步复位,同步释放电路:

-

<snippet>

-

<content><![CDATA[

-

-

//Asynchronous reset, synchronous release

-

-

reg reset_r0, reset_out;

-

-

always@(posedge clk or posedge reset) begin

-

if(reset) begin

-

reset_r0 <= 1;

-

reset_out <= 1;

-

end

-

else begin

-

reset_r0 <= 0;

-

reset_out <= reset_r0;

-

end

-

end

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>reset</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

testbench文件模板:

-

<snippet>

-

<content><![CDATA[

-

-

//Parameter define

-

-

parameter PERIOD = ;

-

-

// Input placed by reg

-

-

reg clk;

-

-

//Output placed by wire

-

-

//Clock Generate

-

-

initial begin

-

clk = 0;

-

forever

-

#(PERIOD/2) clk = ~clk;

-

end

-

-

//Input Design

-

-

initial begin

-

-

-

end

-

-

//Module Instantiation

-

-

MODULE_NAME inst_ ();

-

-

-

]]></content>

-

<!-- Optional: Set a tabTrigger to define how to trigger the snippet -->

-

<tabTrigger>testbench</tabTrigger>

-

<!-- Optional: Set a scope to limit where the snippet will trigger -->

-

<!-- <scope>source.python</scope> -->

-

</snippet>

其他的模板习惯,大家自己定义,暂时就给出这几个比较常用的。

参考文章

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/102553985

- 点赞

- 收藏

- 关注作者

评论(0)