漫谈时序设计(1)跨时钟域是设计出来的,而非约束出来的!

目录

这篇博文在于规范解释一些时序相关的概念,尽管之前也已经写过了很多类似的东西,但今天是站在校招结束的状态下做的一些总结,纯粹是想规范下自己的思路,但同时也会引用到之前相关的博文(点击博文的蓝色字体部分即可跳转)。

今年的应届生求职可能不需要了,但是还有后面的几届呢?

亚稳态(Metastability)

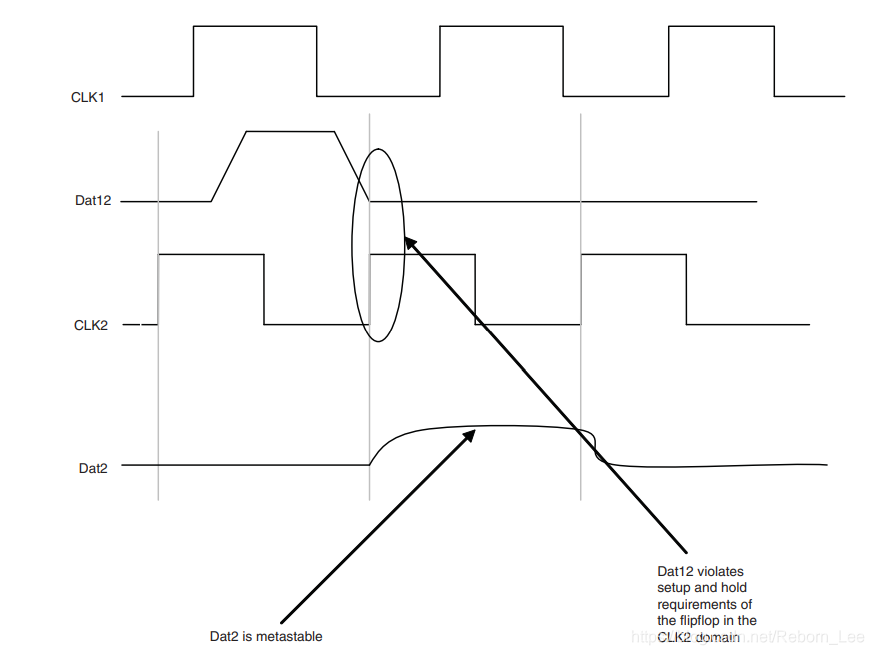

边沿触发器的输出有两种有效的状态,高和低。为了确保电路行为稳定可靠,设计必须满足触发器的建立时间和保持时间。当设计不满足触发器的建立时间和保持时间时,就会出现亚稳态。

亚稳态是触发器的输出在短时间内处于高低震荡,徘徊的状态,但最终会稳定到一个高状态或者低状态。

在多时钟设计中,要确保信号在跨时钟域设计时被正确的同步。典型的设计方式有,同步器、握手机制、或者FIFO。

引用:

The output of an edge-triggered flipflop has two valid states: high and low. To ensure reliable operation, designs must meet flipflop timing requirements for both setup and hold. Whenever a signal violates the setup and hold requirements of a flipflop, the output of the flipflop can be metastable. Metastable outputs oscillate, or hover, between high and low states for a brief period of time and eventually settle down to either a low state or high state. This can cause the system to fail. In multi-clock designs, ensure that signals crossing clock domains are properly synchronized. Typically, this involves using a synchronizer, a handshake mechanism, or a FIFO.

单比特信号同步

慢时钟域到快时钟域

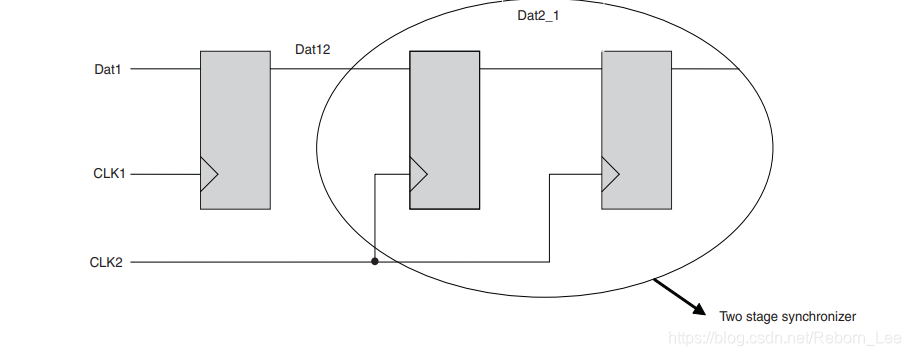

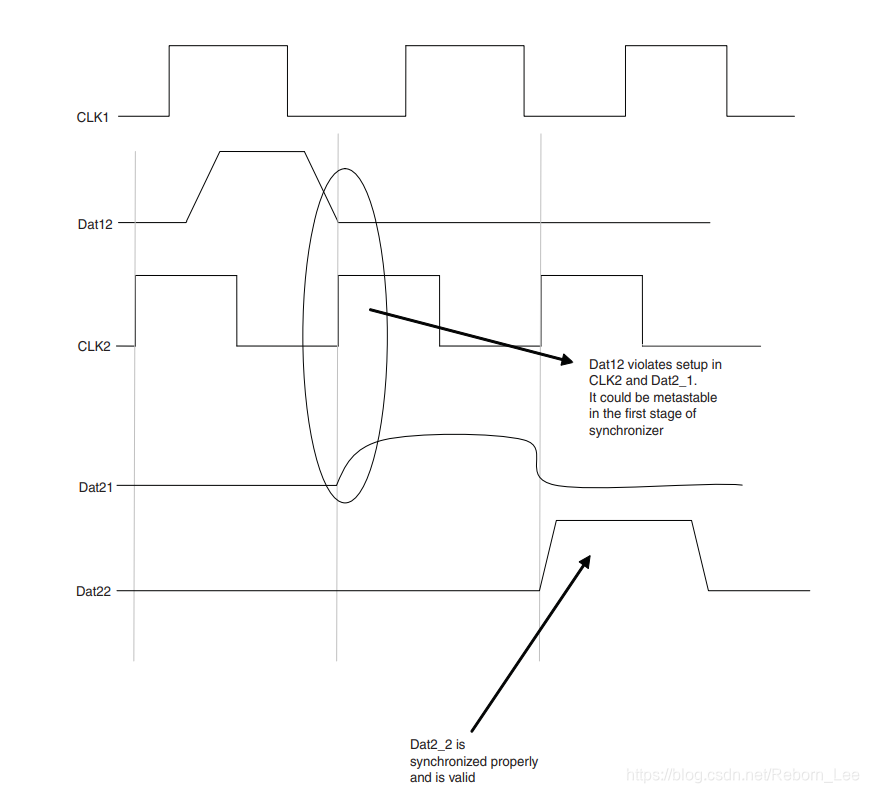

这里的同步器指的是单比特同步器,单比特同步器使用两级寄存器同步的方式实现,也就是通常所说的 “打两拍”。

需要注意的是单比特同步器的使用适用于从慢时钟域到快时钟域的跨时钟域信号传输,不适用于从快到慢的跨时钟域数据传输,原因是快时钟域的单比特信号存在着满时钟域采样不到的情况,这可能使得脉冲过短的信号无法同步到慢时钟域。

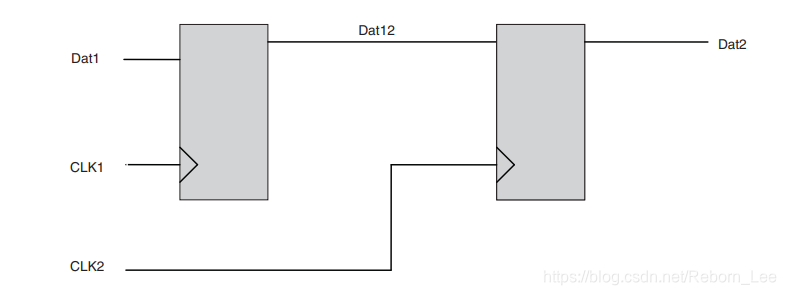

下图给出了一个不满足触发器建立时间的例子,这样会导致第二级触发器的输出出现亚稳态:

如何解决输出出现亚稳态的情况呢?采样如下两级寄存器同步,也即同步器的方式解决:

跨时钟域传输可能出现的问题,是通过设计来解决的,不是通过约束来解决的,因此对于跨时钟域传输的路径,在静态时序分析中叫做Inter-Clock Path,我们对其直接设置伪路径即可,属于时序例外,不需要进行时序分析。

快时钟域到慢时钟域

刚才所说的同步器,也即两级同步器或两阶同步器,使用两级触发器同步,针对的是从慢时钟域到快时钟域的单比特信号跨时钟域传输,但对于从快时钟域到慢时钟域,如何进行跨时钟域传输呢?

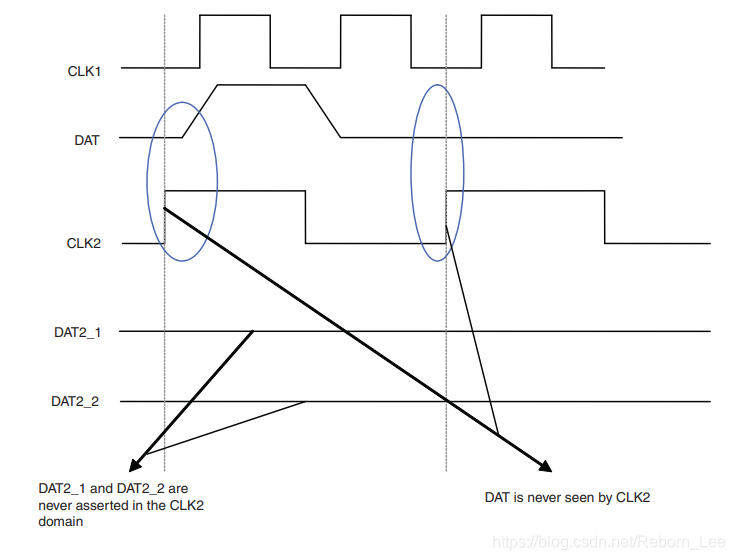

前面也说了,如果使用前面直接两级同步的方式,可能导致快时钟域内过短的脉冲被滤除,也即慢时钟域触发器采样(捕获)不到,导致同步错误,如下示意图:

如何解决这种设计问题呢?

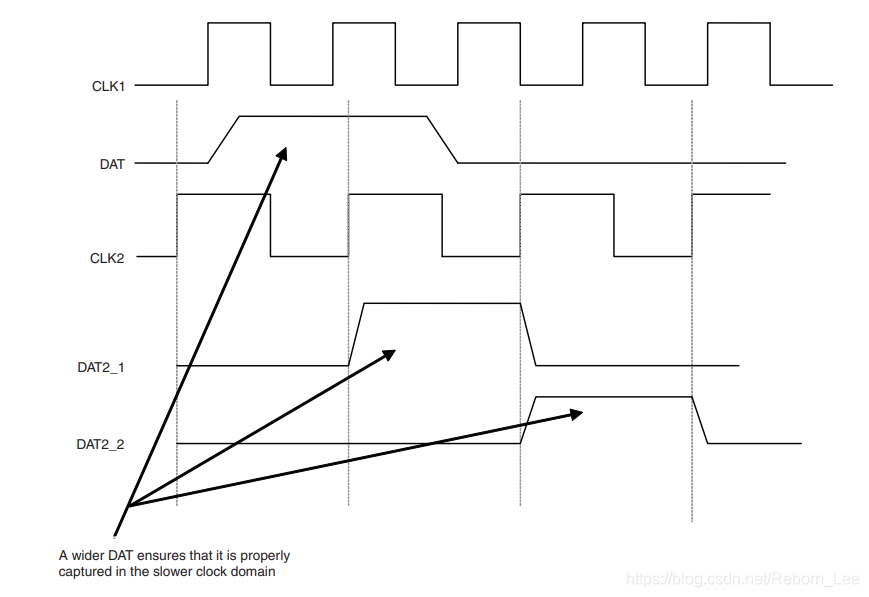

一个简单的思路就是确保快时钟域内的信号有效时间超过慢时钟域的一个周期,如下图:

思路是有了,但是具体的操作呢?

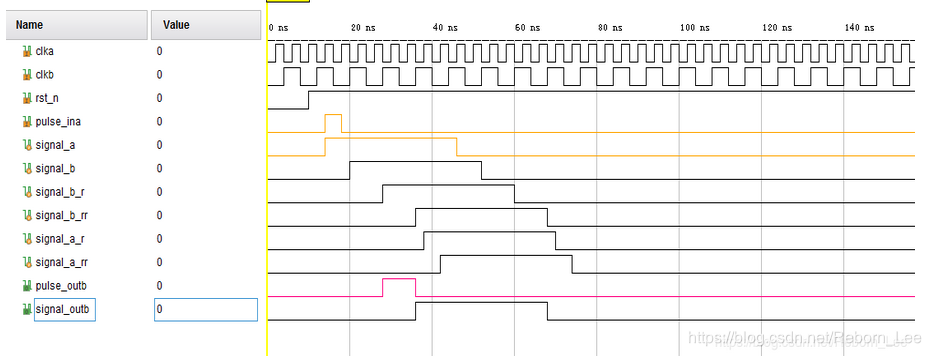

之前的博文介绍了一种方式,就是快时钟域信号电平展宽的方式:

多比特信号同步

多比特信号不是由单比特信号构成的吗?那能不能采样两级寄存器的方式来处理多比特信号的跨时钟域处理呢?

这些问题的答案很坚决?

不可以!

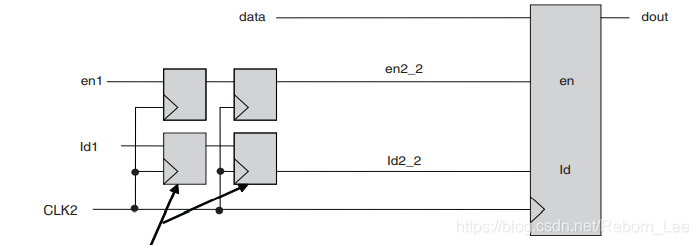

如下图:

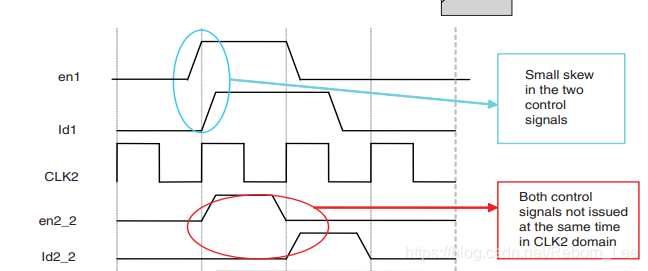

en1和ld1同时跨时钟域传输到CLK2时钟域下:

A small skew, due to either board or PVT variations on the two control signals (Id1 and en1) in the CLK1 clock domain, can cause incorrect data (or no data) to be loaded in the register in the CLK2 clock domain.

意思是两个比特位之间的一点儿偏斜(可能是板子以及PVT干扰)都会导致信号传输错误,如下示意图:

多比特信号也会出现这样的问题。

因此,如何解决多比特信号的跨时钟域传输呢?

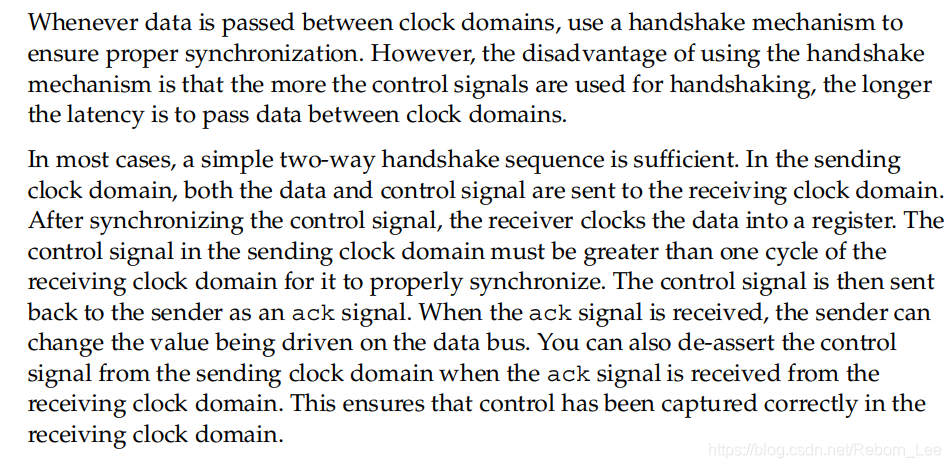

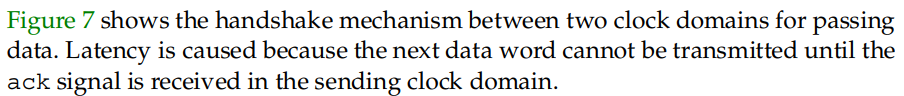

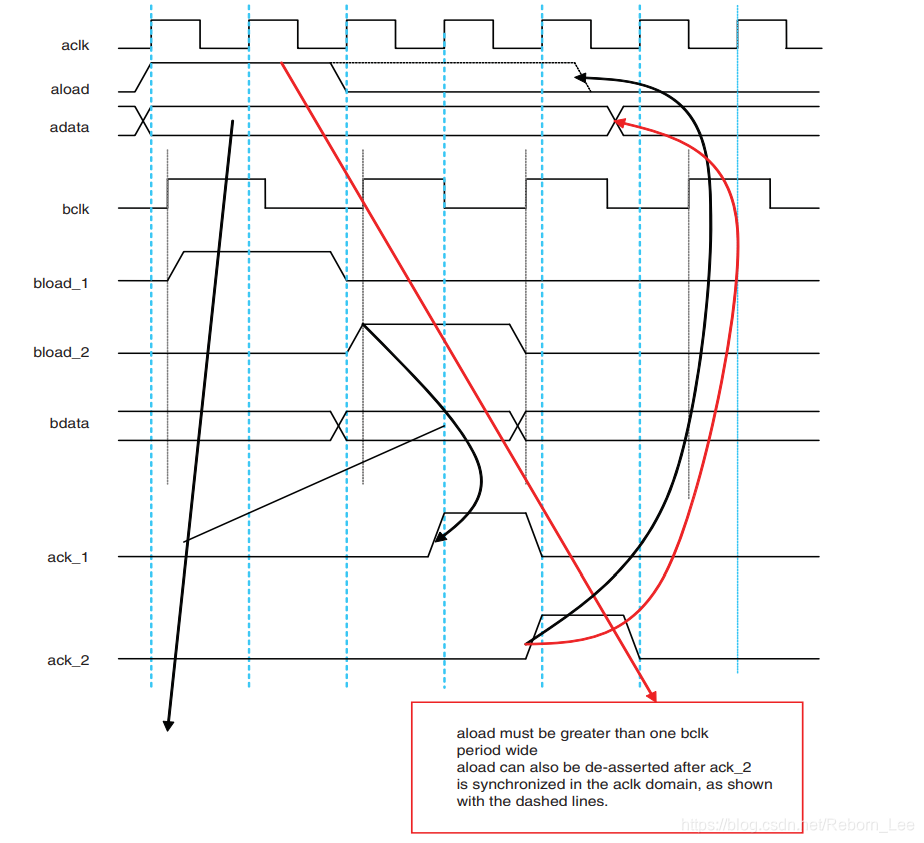

Handshake Mechanism

下面的说法挺好:

异步FIFO

参考链接

参考链接都在文章中的蓝色字体部分,直接点击即可进去。

此外还有:https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an545.pdf

写在最后

在今年的秋招一开始,我就建立了一个微信群,在CSDN发布了一条博文,召集全国各地的同行朋友们共同加入,共同讨论秋招求职笔试,面试经验,目前已经有300多人加入,各位才华横溢,让我大开眼界。

到今天11月份,从西北地区最早结束到其他各地陆续结束,但是我们曾开玩笑说,本群继续召集下一届同行,作为先行者的我们也会对你们给予应有的帮助,欢迎加入,到你们晒工资的时候,会不会再次把我们倒挂呢?拭目以待。

由于人数较多,所以加我的时候务必备注:CSDN+地区或学校+职位(意向职位)+昵称。

我的微信号是:ljs521615

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/102877679

- 点赞

- 收藏

- 关注作者

评论(0)