遇见BUG(1):都是非时钟专用引脚惹的祸?

最近遇到一个问题,就是在使用FPGA上的一对差分时钟的时钟,总是提示这样的错误:

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets i_pl/i_pll/i_mea_lx_pll_wrp/iclk2_ibufg] >

当然是类似这样的error,很疑惑,这对时钟我正常使用,为什么就出现问题了呢?

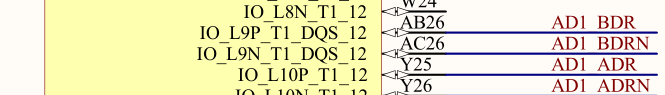

查看电路图:

如上图,AD1_ADR以及AD1_BDR都是时钟引脚,外部时钟从这个引脚上进入FPGA,之后FPGA设计中使用其中的一对时钟。

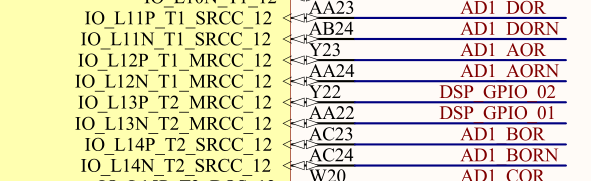

可以看出,上面的这两队时钟信号,对应到FPGA的引脚不是时钟专用引脚,而是普通引脚,这就是问题的根源,我们一般在电路图的设计中,总要将时钟接到FPGA的专用时钟引脚上,例如:

上图中的MRCC,以及SRCC,可以供时钟引脚使用。

由此看来,出现这样的原因是电路设计的锅?

但是呢?我们也不能抱怨,问题并不是说我们做FPGA设计的束手无策,这样的设计,也许是无心的,但是有时候也存在这样情况,例如时钟比较多,时钟专用引脚不够,怎么办呢?

只能用普通IO来接时钟,我们如何在FPGA设计中解决这个问题?

其实仔细看人家提示的错误就好了,人家说了,你可以通过加约束解决这个问题:

如:

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets i_pl/i_pll/i_mea_lx_pll_wrp/iclk2_ibufg] >

把这条提示加入XDC约束文件里面即可,原理就是绕过PAR的检查,但是没有解决根本问题。

最后给出参考链接:

Sub-optimal placement for a clock-capable IO pin and PLL pair

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair

FPGA的LVDS电平以及LVDS25电平能在HR Bank上使用吗?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/102943738

- 点赞

- 收藏

- 关注作者

评论(0)