HDLBits 系列(6)(Reduction)缩位运算符

目录

抛砖引玉

您已经熟悉两个值之间的按位运算,例如a&b或a ^ b。 有时,如果向量很长,您想创建一个对一个向量的所有位进行操作的宽门,例如(a [0]&a [1]&a [2]&a [3] ...)。

缩位运算符可以对向量的位进行AND,OR和XOR,产生一位输出:

&a [3:0] // AND:a [3]&a [2]&a [1]&a [0]。 相当于(a [3:0] == 4'hf)

| b [3:0] //或:b [3] | b [2] | b [1] | b [0]。 相当于(b [3:0]!= 4'h0)

^ c [2:0] // XOR:c [2] ^ c [1] ^ c [0]

这些是只有一个操作数的一元运算符(类似于NOT运算符!和〜)。 您还可以反转这些输出以创建NAND,NOR和XNOR门,例如(〜&d [7:0])。

上述操作中,可以用相应的其他方法来等效替代缩位运算,但是如果位数较多,你怎么做呢?可见,缩位运算符,必不可少。

例如:

Build a combinational circuit with 100 inputs, in[99:0].

There are 3 outputs:

- out_and: output of a 100-input AND gate.

- out_or: output of a 100-input OR gate.

- out_xor: output of a 100-input XOR gate.

此时,用缩位运算符就比较方便:

-

module top_module(

-

input [99:0] in,

-

output out_and,

-

output out_or,

-

output out_xor

-

);

-

assign out_and = ∈

-

assign out_or = |in;

-

assign out_xor = ^in;

-

-

endmodule

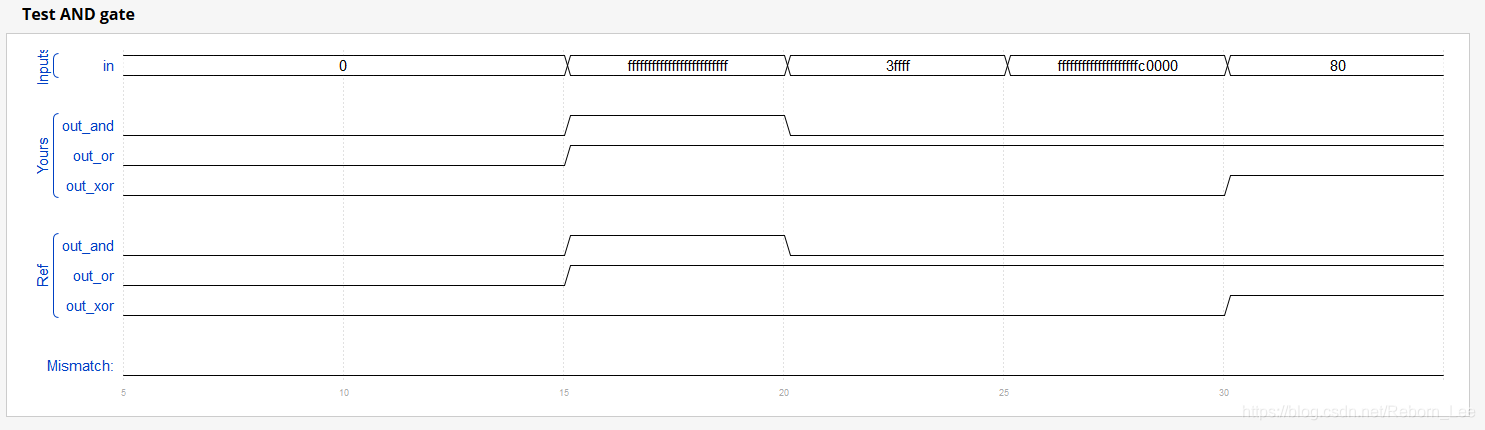

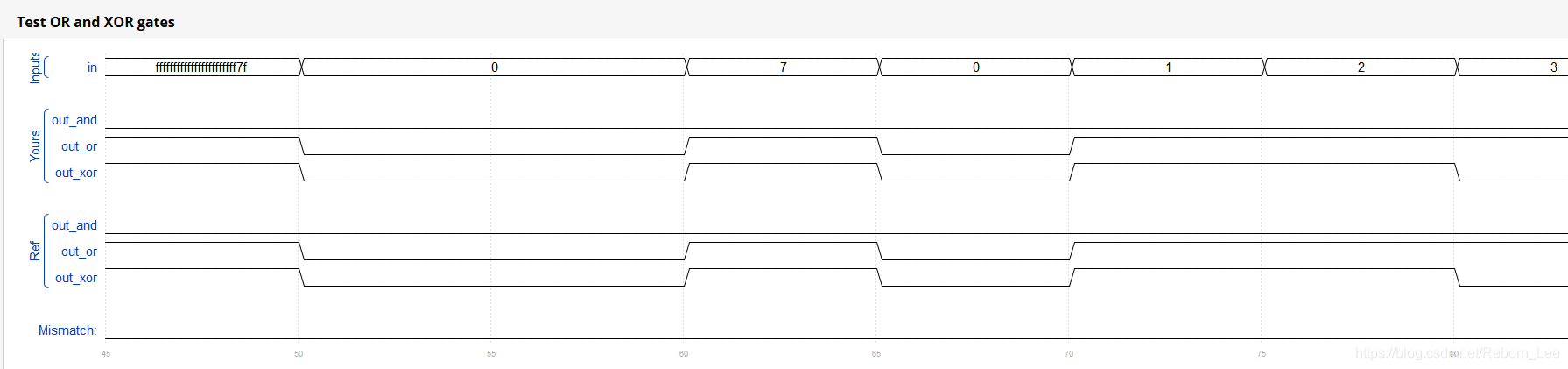

代入HDLBits中验证:

Reduction在奇偶校验中的应用

通过不完善的通道传输数据时,奇偶校验通常用作检测错误的简单方法。 创建一个电路,该电路将计算8位字节的奇偶校验位(这将在字节中添加第9位)。 我们将使用“偶数”奇偶校验,其中奇偶校验位只是所有8个数据位的XOR。

对于偶校验来说,通过将所有校验位进行异或,如果最后结果为1,则代表传输无误,否则有误。

这是什么意思呢?

如果一个变量中有偶数位1,则所有位进行异或,肯定得到1,否则得到0;

如下进行验证:

-

module top_module (

-

input [7:0] in,

-

output parity);

-

assign parity = ^in;

-

-

endmodule

很简单,缩位运算符很方便,如果能在该用它的地方用到它,会简化很多。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103204171

- 点赞

- 收藏

- 关注作者

评论(0)