HDLBits 系列(5)让三元条件运算符(?:)在你的设计中发挥作用

目录

抛砖引玉

Verilog具有三元条件运算符(?:)运用得当,可以起到简化代码的作用,使得代码的易读性提高,但是运用不当,也会背道而驰。

下面讲讲Verilog具有三元条件运算符(?:)的一些用途?

Verilog具有三元条件运算符(?:),非常类似于C:

(condition ?if_true:if_false)

可以用于根据一行上的条件(多路复用器!)选择两个值之一,而无需在组合的always块中使用if-then。

Examples:

可用于二选一:

(0 ? 3 : 5) // This is 5 because the condition is false. (sel ? b : a) // A 2-to-1 multiplexer between a and b selected by sel. 可用于时序逻辑: always @(posedge clk) // A T-flip-flop. q <= toggle ? ~q : q; 可用于状态机的状态转换逻辑中: always @(*) // State transition logic for a one-input FSM case (state) A: next = w ? B : A; B: next = w ? A : B; endcase 可用于三态缓冲器: assign out = ena ? q : 1'bz; // A tri-state buffer 可以构成更复杂的三选一的多路选择器: ((sel[1:0] == 2'h0) ? a : // A 3-to-1 mux (sel[1:0] == 2'h1) ? b : c )

举例练习

给你四个无符号数,找出最小值。

这个问题本来是在C语言中最简单的题目了,这里用电路的方式来设计出来,下面是具体描述:

给定四个无符号数字,找到最小值。 可以将无符号数字与标准比较运算符(a <b)进行比较。 使用条件运算符创建双向最小回路,然后组合其中的一些以创建四向最小回路。 您可能需要一些线向量来获得中间结果。

预期的解决方案长度:大约5行。

你会怎么做呢?

我们做逻辑设计的,可不能用什么软件思维去设计电路,用当年学的C语言来冒泡排序来解决这个问题,双重循环?

恐怕你是来搞笑的。

下面给出我的设计:

-

module top_module (

-

input [7:0] a, b, c, d,

-

output [7:0] min);//

-

-

// assign intermediate_result1 = compare? true: false;

-

wire [7:0] min1, min2, min3;

-

assign min1 = (a > b)? b : a;

-

assign min2 = (min1 > c)? c : min1;

-

assign min3 = (min2 > d)? d : min2;

-

assign min = min3;

-

endmodule

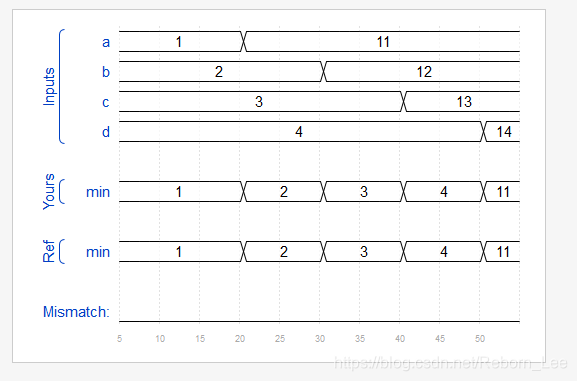

代入HDLBits来验证结果:

写在最后

在今年的秋招一开始,我就建立了一个微信群,在CSDN发布了一条博文,召集全国各地的同行朋友们共同加入,共同讨论秋招求职笔试,面试经验,目前已经有300多人加入,各位才华横溢,让我大开眼界。

到今天11月份,从西北地区最早结束到其他各地陆续结束,但是我们曾开玩笑说,本群继续召集下一届同行,作为先行者的我们也会对你们给予应有的帮助,欢迎加入,到你们晒工资的时候,会不会再次把我们倒挂呢?拭目以待。

由于人数较多,所以加我的时候务必备注:CSDN+地区或学校+职位(意向职位)+昵称。

我的微信号是:ljs521615

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103202320

- 点赞

- 收藏

- 关注作者

评论(0)