HDLBits 系列(4)如何设计一定不会产生Latch的组合逻辑?

目录

抛砖引玉

假设您正在建立一个电路来处理游戏的PS / 2键盘的扫描代码(scancodes)。给定收到的扫描码(scancodes)的最后两个字节,您需要指示是否已按下键盘上的箭头键之一。这涉及到相当简单的映射,可以将其实现为具有四个案例的case语句(或if-elseif)。

| Scancode [15:0] | Arrow key |

|---|---|

| 16'he06b | left arrow |

| 16'he072 | down arrow |

| 16'he074 | right arrow |

| 16'he075 | up arrow |

| Anything else | none |

您的电路具有一个16位输入和四个输出。建立识别这四个扫描码(scancodes)并有效正确输出的电路。

为避免创建锁存器,必须在所有可能的情况下为所有输出分配一个值。仅仅具有默认情况是不够的。您必须在所有四种情况和默认情况下为所有四个输出分配一个值。这可能涉及许多不必要的输入。解决此问题的一种简单方法是在case语句之前为输出分配“默认值”:

always @(*) begin up = 1'b0; down = 1'b0; left = 1'b0; right = 1'b0; case (scancode) ... // Set to 1 as necessary. endcase end

这种代码风格可确保在所有可能的情况下为输出分配一个值(0),除非case语句覆盖该分配。这也意味着默认:case项变得不必要。

个人总结

上面这个问题说的是在case之前给输出一些默认值,这其实也是我一直以来的做法,在Verilog高级数字系统设计技术与实例分析这本书中,大量的设计运用了这种风格的代码。

这么做的好处在于:

首先永远不会产生锁存器,因为我的输出有了默认值,每一种情况下,如果没有case下面的条件覆盖,则都会有默认值,于是乎也就不存在有写情况下输出没有给具体值的情况了,自然锁存器也不会生成了。

对于上面这个问题,我们相应的代码设计可以像这样:

-

// synthesis verilog_input_version verilog_2001

-

module top_module (

-

input [15:0] scancode,

-

output reg left,

-

output reg down,

-

output reg right,

-

output reg up );

-

always@(*)begin

-

// left = 0;

-

// down = 0;

-

//right = 0;

-

// up = 0;

-

case(scancode)

-

16'he06b: left = 1;

-

16'he072: down = 1;

-

16'he074: right = 1;

-

16'he075: up = 1;

-

endcase

-

end

-

-

endmodule

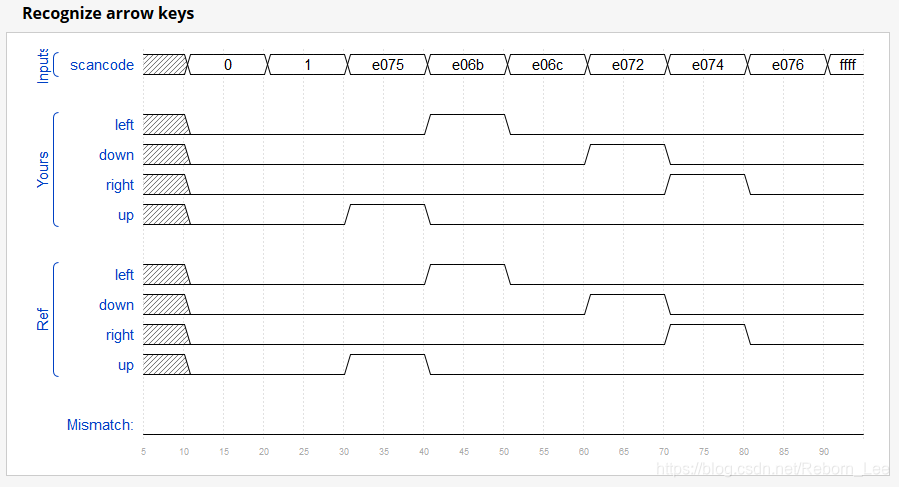

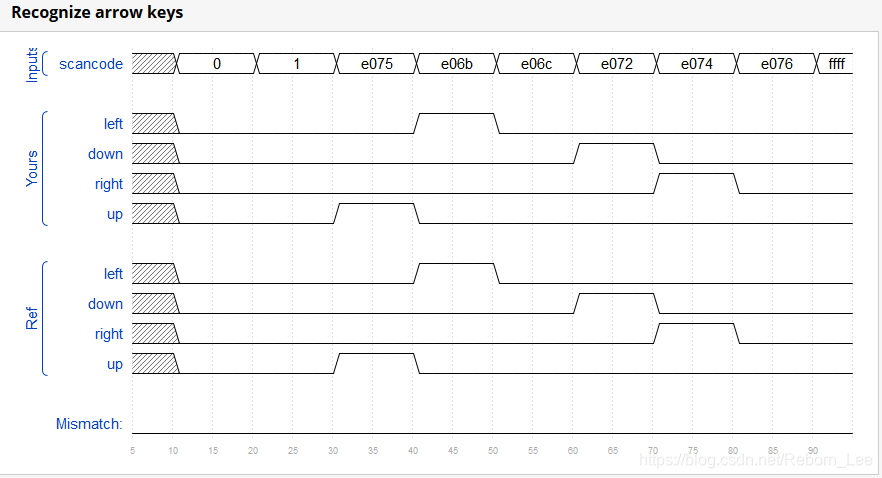

代入HDLBits中验证:

麻烦的设计

如果不给默认值,我们可以这么设计:

-

// synthesis verilog_input_version verilog_2001

-

module top_module (

-

input [15:0] scancode,

-

output reg left,

-

output reg down,

-

output reg right,

-

output reg up );

-

always@(*)begin

-

case(scancode)

-

16'he06b: begin

-

left = 1;

-

down = 0;

-

right = 0;

-

up = 0;

-

end

-

16'he072: begin

-

left = 0;

-

down = 1;

-

right = 0;

-

up = 0;

-

end

-

-

16'he074: begin

-

left = 0;

-

down = 0;

-

right = 1;

-

up = 0;

-

end

-

16'he075: begin

-

left = 0;

-

down = 0;

-

right = 0;

-

up = 1;

-

end

-

default: begin

-

left = 0;

-

down = 0;

-

right = 0;

-

up = 0;

-

end

-

-

endcase

-

end

-

-

endmodule

虽然也能实现同样的功能,但是是不是很麻烦呢?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103201531

- 点赞

- 收藏

- 关注作者

评论(0)