HDLBits 系列(13) All about DFF

目录

终于到了时序逻辑的部分,但是有些设计是最最基础的,多说一句话都多,所以只是列出来,到了适当的时候,会给出说明。

DFF

D触发器是一种存储位的电路,并在时钟信号的(通常)上升沿定期进行更新。

Verilog描述:

-

module top_module (

-

input clk, // Clocks are used in sequential circuits

-

input d,

-

output reg q );//

-

always@(posedge clk)begin

-

q <= d;

-

end

-

-

// Use a clocked always block

-

// copy d to q at every positive edge of clk

-

// Clocked always blocks should use non-blocking assignments

-

-

endmodule

Dff8

Create 8 D flip-flops. All DFFs should be triggered by the positive edge of clk.

-

module top_module (

-

input clk,

-

input [7:0] d,

-

output [7:0] q

-

);

-

always@(posedge clk) begin

-

q <= d;

-

end

-

-

endmodule

多Bit的DFF可以称之为寄存器。

Dff8r

Create 8 D flip-flops with active high synchronous reset. All DFFs should be triggered by the positive edge of clk.

-

module top_module (

-

input clk,

-

input reset, // Synchronous reset

-

input [7:0] d,

-

output [7:0] q

-

);

-

always@(posedge clk) begin

-

if(reset) q <= 0;

-

else q <= d;

-

end

-

-

endmodule

确定复位值的DFF

-

module top_module (

-

input clk,

-

input reset,

-

input [7:0] d,

-

output [7:0] q

-

);

-

always@(negedge clk) begin

-

if(reset) q <= 8'h34;

-

else q <= d;

-

-

end

-

-

endmodule

-

Dff8ar

-

module top_module (

-

input clk,

-

input areset, // active high asynchronous reset

-

input [7:0] d,

-

output [7:0] q

-

);

-

always@(posedge clk or posedge areset) begin

-

if(areset) q <= 0;

-

else q <= d;

-

end

-

-

endmodule

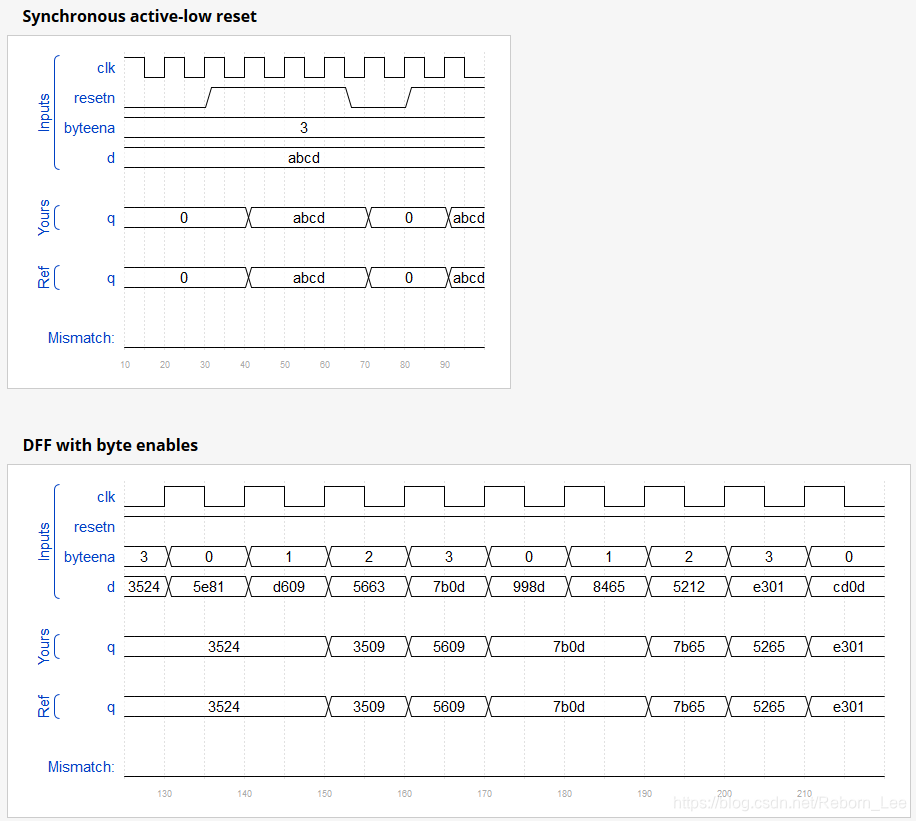

Dff16e

创建16个D触发器。 有时只修改一组触发器的一部分。 字节使能输入控制是否应在该周期内写入16个寄存器的每个字节。 byteena [1]控制高字节d [15:8],而byteena [0]控制低字节d [7:0]。

resetn是同步,低电平有效复位。

所有DFF应由clk的上升沿触发。

这一题就有点意思了,用使能控制信号控制时钟上升沿到来时候,改变输出的哪一个字节。

根据题目描述,我们需要考虑全部情况才是,仅仅0为有效,更新低字节;仅仅1位有效,更新高字节;二者都有效,全部更新;否则,保持不变;

下面是我的设计:

-

module top_module (

-

input clk,

-

input resetn,

-

input [1:0] byteena,

-

input [15:0] d,

-

output [15:0] q

-

);

-

always@(posedge clk) begin

-

if(~resetn) q <= 0;

-

else if(byteena[0]&~byteena[1]) q[7:0] <= d[7:0];

-

else if(~byteena[0]&byteena[1]) q[15:8] <= d[15:8];

-

else if(byteena[0]&byteena[1]) q <= d;

-

else ;

-

end

-

-

endmodule

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103226382

- 点赞

- 收藏

- 关注作者

评论(0)