HDLBits 系列(18) BCD码计数器的设计

目录

原题复现

先给出原题:

建立一个4位数的BCD(二进制编码的十进制)计数器。 每个十进制数字使用4位编码:q [3:0]是个位,q [7:4]是十位,依此类推。对于数字[3:1],还输出一个使能信号,指示每个高三位应递增。

也就是:

设计一个4位BCD(二进制编码十进制)计数器。每个十进制数字使用4-bit来表示:q[3:0]是个位,q[7:4]是十位等。对于ena[3:1],该信号用来表示个位、十位和百位的进位。

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

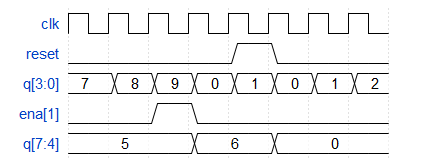

时序图如下:

审题

我来解释下这个题目的意思,就是设计一个4位的十进制计数器,分别为个位,十位,百位,千位;

然后个位进位,十位进位,百位进位时,都输出一个使能信号。

通过例化一个4bit的BCD码计数器实现。

我的设计

既然如此,我们先设计一个4bit的BCD码计数器,一定要带有使能:

-

module count4

-

(

-

input clk,

-

input reset,

-

input ena,

-

output reg[3:0] q

-

);

-

-

always @ (posedge clk)

-

begin

-

if(reset)

-

q <= 4'b0;

-

else if (ena)

-

begin

-

if(q == 4'd9)

-

q <= 4'd0;

-

else

-

q <= q + 1'b1;

-

end

-

end

-

-

endmodule

之后通过例化这个4bit的BCD码计数器得到一个16bit的BCD码计数器:

个位永远使能,十位要等到个位计数到9之后使能,百位要等到个位和十位都等于9的时候使能,同理,千位要等到个位、十位、百位都等于9的时候使能。

于是得到如下设计:

-

module top_module (

-

input clk,

-

input reset, // Synchronous active-high reset

-

output [3:1] ena,

-

output [15:0] q);

-

-

-

-

-

wire en1, en2, en3, en4;

-

assign en1 = 1;

-

assign en2 = (q[3:0] == 4'd9);

-

assign en3 = (q[7:4] == 4'd9 && q[3:0] == 4'd9);

-

assign en4 = (q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9);

-

-

-

//one

-

count4 inst1_count4

-

(

-

.clk(clk),

-

.reset(reset),

-

.ena(en1),

-

.q(q[3:0])

-

);

-

-

//ten

-

count4 inst2_count4

-

(

-

.clk(clk),

-

.reset(reset),

-

.ena(en2),

-

.q(q[7:4])

-

);

-

-

//hundred

-

count4 inst3_count4

-

(

-

.clk(clk),

-

.reset(reset),

-

.ena(en3),

-

.q(q[11:8])

-

);

-

-

//thousand

-

count4 inst4_count4

-

(

-

.clk(clk),

-

.reset(reset),

-

.ena(en4),

-

.q(q[15:12])

-

);

-

-

//用来表示进位

-

assign ena = {q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9, q[7:4] == 4'd9 && q[3:0] == 4'd9, q[3:0] == 4'd9};

-

-

endmodule

参考链接:Problem 104 4-digit decimal counter

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103240708

- 点赞

- 收藏

- 关注作者

评论(0)