HDLBits 系列(34)Serial two's complememter(Mealy and Moore FSM)

目录

Mealy 状态机

原题复现

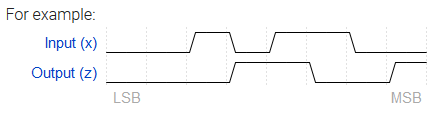

The following diagram is a Mealy machine implementation of the 2's complementer. Implement using one-hot encoding.

尽管我不太清楚这是个为啥?

但既然状态转移图都给你了,设计一个mealy状态机应该不成问题:

我的设计

-

module top_module (

-

input clk,

-

input areset,

-

input x,

-

output z

-

);

-

-

localparam A = 2'b01, B = 2'b10;

-

reg [1:0] state, next_state;

-

always@(*)begin

-

case(state)

-

A: begin

-

if(x) next_state = B;

-

else next_state = A;

-

end

-

B: begin

-

next_state = B;

-

end

-

default: begin

-

next_state = A;

-

end

-

endcase

-

end

-

-

always@(posedge clk or posedge areset) begin

-

if(areset) state <= A;

-

else state <= next_state;

-

end

-

-

assign z = (state == A)?x:~x;

-

-

/*

-

reg z_mid;

-

always@(*)begin

-

case(state)

-

A: begin

-

if(x) z_mid = 1;

-

else z_mid = 0;

-

end

-

B: begin

-

if(x) z_mid = 0;

-

else z_mid = 1;

-

end

-

default: begin

-

z_mid = 0;

-

end

-

endcase

-

end

-

-

assign z = z_mid;

-

*/

-

-

endmodule

Moore 状态机

姊妹篇,用Moore状态机如何实现?

原题复现

You are to design a one-input one-output serial 2's complementer Moore state machine. The input (x) is a series of bits (one per clock cycle) beginning with the least-significant bit of the number, and the output (Z) is the 2's complement of the input. The machine will accept input numbers of arbitrary length. The circuit requires an asynchronous reset. The conversion begins when Reset is released and stops when Reset is asserted.

状态转移图

我们根据mealy状态机的状态转移图来画Moore状态机的状态转移图,然后完成设计。

我的设计

给出设计:

-

module top_module (

-

input clk,

-

input areset,

-

input x,

-

output z

-

);

-

-

localparam A = 0, B = 1, C = 2, D = 3;

-

reg [1:0] state, next_state;

-

always@(*) begin

-

case(state)

-

A: begin

-

if(x) next_state = B;

-

else next_state = A;

-

end

-

B: begin

-

if(x) next_state = D;

-

else next_state = C;

-

end

-

C: begin

-

if(x) next_state = D;

-

else next_state = C;

-

end

-

D: begin

-

if(x) next_state = D;

-

else next_state = C;

-

end

-

default: begin

-

next_state = A;

-

end

-

-

endcase

-

end

-

always@(posedge clk or posedge areset) begin

-

if(areset) state <= A;

-

else state <= next_state;

-

end

-

-

assign z = (state == B || state == C)? 1 : 0;

-

-

-

-

endmodule

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103454958

- 点赞

- 收藏

- 关注作者

评论(0)