HDLBits 系列(42)根据仿真波形来设计电路之时序逻辑

前言

上篇博文讨论了组合逻辑的情况,最后留了几个题目,我也没做,感觉繁杂,有兴趣的可以挑战一下,地址为:

上篇博文链接

这篇博客,可以说是上篇博客的姊妹篇,简单的讨论下时序逻辑的类型,通过仿真波形来设计电路是一类题目,也应该是我们应该具备的电路设计能力。

写代码心里要有电路,给出电路要能转化为设计,给出波形图也要能给出电路设计,这都是需要努力的方向。

电路设计1

先给出一个最简单的时序波形,然后给出设计。

原题链接

原题复现

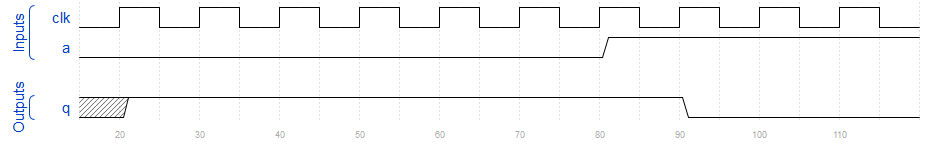

This is a sequential circuit. Read the simulation waveforms to determine what the circuit does, then implement it.

题目解析

很容易看出,这仅仅是对输入延迟一拍,并取反得到最后的结果。

我的设计

module top_module ( input clk, input a, output q ); reg q_r1 = 0; always@(posedge clk) begin q_r1 <= a; end assign q = ~q_r1;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

电路设计2

原题复现

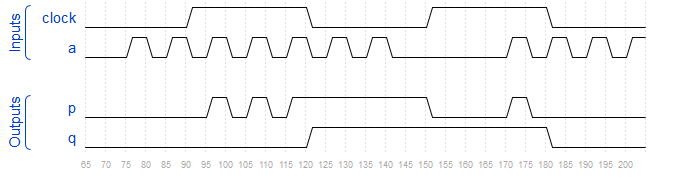

This is a sequential circuit. Read the simulation waveforms to determine what the circuit does, then implement it.

题目解析

这个题目还是需要多看一会的,对于p来说是一个时钟高电平跟随,低电平锁存的锁存器。

对于q是一个二分频电路,注意,是在时钟下降沿的时候,q翻转一次。

不得不让人吐槽的是,没有给出复位信号,所以我们只能在信号定义的时候给一个初值,至于初值是0还是1,没有要求,但是如果是做这个题目,就可能对应其中的一种。

在波形信息中,我只能看到这一点。如果设计还是不正确的话,就让这道题去si吧,心里知道怎么回事就好了,不得不说bug一条。

我的设计

module top_module ( input clock, input a, output p, output q ); reg p_mid = 0; always@(*)begin if(clock) p_mid = a; else p_mid = p_mid; end reg q_mid = 1; always@(negedge clock) begin q_mid <= ~q_mid; end assign q = q_mid; assign p = p_mid;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

电路设计3

原题复现

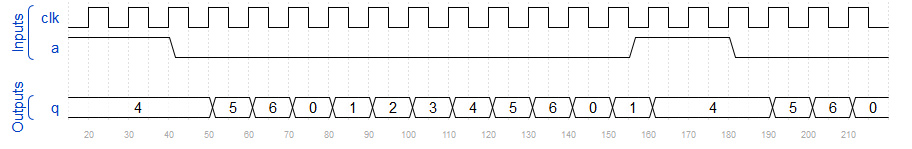

This is a sequential circuit. Read the simulation waveforms to determine what the circuit does, then implement it.

Module Declaration

module top_module (

input clk,

input a,

output [3:0] q );

题目解析

这个题目其实就是一个带有使能的计数器,计数值最大为6,使能信号a低电平有效,无效期间置位为4。

我的设计

module top_module ( input clk, input a, output [3:0] q ); reg [3:0] q_mid; always@(posedge clk)begin if(a) q_mid <= 4; else if(q_mid == 6) q_mid <= 0; else q_mid <= q_mid + 1; end assign q = q_mid;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

电路设计4

原题复现

This is a sequential circuit. The circuit consists of combinational logic and one bit of memory (i.e., one flip-flop). The output of the flip-flop has been made observable through the output state.

Read the simulation waveforms to determine what the circuit does, then implement it.

Module Declaration

Module Declaration

module top_module (

input clk,

input a,

input b,

output q,

output state );

题目解析

这个题目暂时没有看出来,等待你的发现。

我的设计

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103539859

- 点赞

- 收藏

- 关注作者

评论(0)