FPGA之道(4)锁存器与寄存器

概念

触发器与这两个称谓之间到底有着什么样的关系呢?

事实上,在我们进行数字电路设计的时候,只需要关注于器件的功能和使用方式即可,而不需要对器件的实现原理和结构进行过多细节方面的了解,因此,通常将电平敏感型的触发器叫做锁存器,而将边沿敏感型的触发器叫做寄存器,并且,通常所说的锁存器,大多是指电平敏感型D触发器,而通常所说的寄存器,大多是指边沿敏感型D触发器。

多位

将多个锁存器或者寄存器并行使用,即可形成多位锁存器或者多位寄存器。这是考虑到现实世界中,需要存储的信息往往是一个bit所不能完全表示的。

多位寄存器的一个典型例子便是计数器,例如我们需要实现一个在0~7之间不断变化的计数器,那么就需要将3个1bit的寄存器并行使用,形成3位寄存器。

阵列

将若干个多位寄存器聚合在一起,形成一维、二维甚至更高维度的结构,便成为了寄存器阵列。这样便可以形成更为复杂的存储结构,从而实现更为复杂的功能。

阵列寄存器中一个典型的例子便是移位寄存器,它是通过将多个寄存器首尾相连得到的,并且根据最开始与最末尾两个寄存器的连接关系,又可分为普通移位寄存器和环形移位寄存器,分别介绍如下:

普通移位寄存器

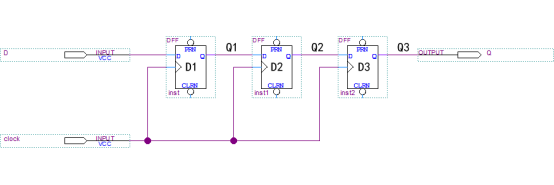

以三级普通移位寄存器为例,它的原理电路图如下:

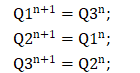

当不使用异步置0、置1信号时,并且假设时钟信号clock是同时到达各个寄存器的,那么结合主从D触发器、维持-阻塞型触D发器或者是边沿触发的JK触发器的脉冲特性来看,当D1的输出还没有来得及更新时,D2的输入已经或恰巧不需要保持稳定了。同理可以分析D3,因此,在clock上升沿到来之时,上图中各个寄存器的状态转换公式为:

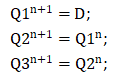

假设D的变化间隔与clock信号的周期一致,那么,上述三级普通移位寄存器的整体状态转换公式可写为:

二、环形移位寄存器。

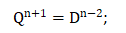

以三级环形移位寄存器为例,它的原理电路图如下:

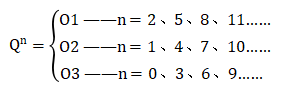

上电后,各个寄存器肯定先被分配了确定的值,那么当不使用异步置0、置1信号时,在clock上升沿到来之时,上图中各个寄存器的状态转换公式为:

若设初始时,各个寄存器的输出分别为O1、O2、O3,那么上述三级环形移位寄存器的整体状态转换公式可写为:

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/104231048

- 点赞

- 收藏

- 关注作者

评论(0)