FPGA之道(8)时钟处理单元

前言

2020年2月10日15:02:18

这个时间的FPGA发展可以说已经很成熟了,Xilinx早已推出了ZYNQ系列,并推出了新工具VITIS 2019.2,当然Vivado并没有淘汰也几乎不可能淘汰,VITIS 2019.2自然也内含了Vivado 2019.2.

对于FPGA中的时钟处理单元,或者说时钟管理单元,在7系列FPGA中,有我们最常见的MMCM以及PLL,这在FPGA工程中,建立时钟IP核时可以清晰的看到。

至于更早期的时钟处理单元,有DCM、PLL等,叫法不同 ,下面根据《FPGA之道》这本书上的描述简单介绍一下。

背景

在实际的使用中,经常会碰到外部送给我们的时钟信号在频率或者相位上并不满足直接使用的要求,而内部时序逻辑又只能对时钟信号进行整数倍的分频,并且不能保证产生新时钟信号的相位稳定性,所以这个时候就需要用到时钟处理单元。

时钟处理单元可以对时钟信号进行高精度的倍频、分频和相位调整,因此对时序逻辑的设计非常重要。FPGA中的时钟处理单元共有两种:PLL和DCM,分别介绍如下:

PLL

PLL,英文全称:Phase Locked Loop,翻译成中文即锁相环。因为PLL调整输入时钟信号频率和相位的原理中利用了模拟电路的知识。因此一般来说,FPGA并不是一个纯粹的数字电路,因为它其中一般会包含PLL,当然,它还会包含一个内部晶振电路用于产生上电自加载时的时钟信号。

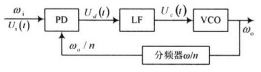

PLL的原理结构框图如下图:

它的原理是这样的:压控振荡器VCO输出的信号为整个锁相环最终的输出信号,该信号会经过一个整数分频器分频后反馈给鉴相器PD(其实也是鉴频器),PD比较该反馈信号与输入的本振信号,如果它们之间有差别,那么PD会输出差别信号,该差别信号经过低通滤波器LF滤波后,形成控制VCO频率变化的控制电压。在该控制电压的作用下,VCO输出信号的频率或相位将改变,如果新的输出信号经过反馈回路后与本振信号相等,那么PLL进入锁定状态,否则PLL仍在失锁状态,上述调整将会继续进行。

Xilinx公司的锁相环结构简介

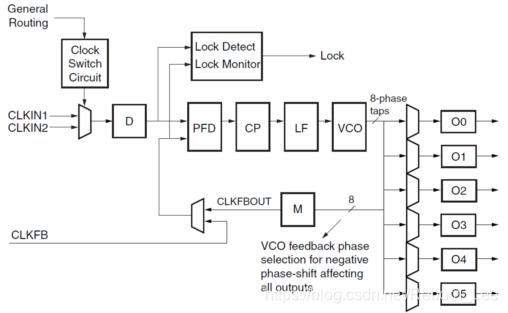

Xilinx公司的锁相环大致结构如下图:

我们可以看出它的核心电路完全遵从PLL的原理结构框图。其中VCO的输出并不直接供给内部逻辑,而是通过相位调整和分频器后再输出,而这样的输出电路组合可以有若干个,所以在它的输出端非常的灵活,每个输出端都可以有不同的频率和相位偏移,当然,频率和相位的调整步进都是由VCO输出信号决定的。

Altera公司的锁相环结构简介

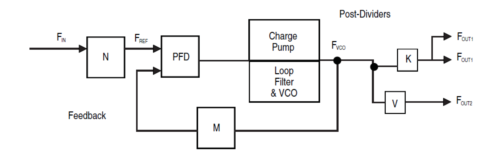

Altera公司的锁相环大致结构如下图:

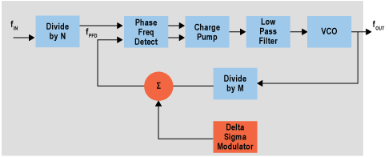

我们可以看出它的核心电路也是完全遵从PLL的原理结构框图的。除此以外,Altera公司还提供了fPLL,即fraction PLL,中文翻译为分数锁相环,它的原理框图如下:

分数锁相环是锁相环的一个分支,传统的锁相环,VCO输出的频率一般都是参考时钟(注意,参考时钟不是输入时钟)的整数倍,为了得到分数倍的输出频率,我们需要在VCO和输出端之间加入分频器,就像Xilinx公司和Altera公司的PLL一样,但是分数锁相环通过在VCO到鉴频鉴相器之间的反馈回路上增加一个微调模块Delta Sigma Modulator,从而实现VCO的输出直接就可以为参考时钟频率的分数倍的功能,从而省略了VCO后端的分频电路。

DCM

DCM,英文全称:Digital Clock Manager,翻译成中文即数字时钟管理员。与PLL不同,DCM并没有利用模拟电路的原理,而是采用了全数字的处理方式实现时钟信号的处理。DCM中的一个核心结构为DLL,英文全称为delay-locked loop,翻译成中文应该是延迟锁定环,因此,它的原理与PLL有着本质的不同。目前,DLL的技术被Xilinx公司所垄断,因此也只有Xilinx公司的FPGA芯片中会有DCM模块,不过随着PLL的快速发展,DLL由于其一些先天的缺陷慢慢失去了优势,因此,如果Xilinx公司无法在短期内在DLL的技术上有所突破的话,那么以后DCM模块很可能会被淘汰。不过就现在来说,DCM还是可以胜任绝大多数设计情况的。以下是DLL的一个原理概念图:

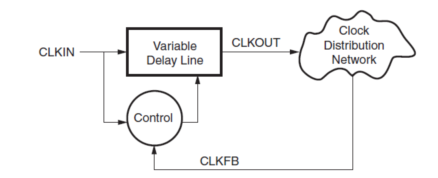

其中Varaible Delay Line是一个可变的延迟线,内部应该是由若干个小的延迟单元或者缓冲门组成,而Control模块通过比较CLKIN和CLKFB的相位关系,对可变延迟线的延迟时间进行调整,直到CLKIN和CLKFB的相位相差达到360度(其实就是一度不差)后完成锁定。

由于Xilinx并没有公布DCM的技术细节,所以还有很多内容我们不得而知。不过从功能上来讲,DCM与PLL类似,也可以实现对时钟信号进行高精度的倍频、分频和相位调整。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/104248952

- 点赞

- 收藏

- 关注作者

评论(0)