FPGA之道(36)Verilog中的编译指令

前言

本文摘自《FPGA之道》,一起来了解下Verilog中的编译指令。

Verilog中的编译指令

为了方便我们对程序编译、仿真时的控制,Verilog提供了很多编译指令,这里主要介绍几种比较常用的编译指令。注意,编译指令都不需要在结尾加类似分号这样的结束符号,只需要换行即可。

define指令

define指令有四种语法:

语法一:`define <name> <string>

- 1

它可以用来定义参数,功能和parameter类似,例如:

`define WIDTH 8

reg [`WIDTH-1:0] data;

- 1

- 2

语法二:`define <name>

- 1

它只是表示定义了一个名为的变量,具体用法参看语法四。

语法三:

`ifndef <define_name> <statements>;

`endif

- 1

- 2

- 3

该语法表示,如果名为<define_name>的变量被定义了,那么就将在编译的时候将的内容包含进来,否则不编译这部分内容。我们可以看出条件编译指令的作用跟条件生成语句比较类似,具体用法参看语法四。

语法四:

`ifdef <define_name0>

<statements>;

`elsif <define_name1>

<statements>;

<other branchs>

`else

<statements>;

`endif

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

该语法是条件编译语法的完全形式,用法举例如下:

- 1

`define AND

`ifdef AND

assign c = a & b;

`elsif OR

assign c = a | b;

`else

assign c = a;

`endif

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

由于AND已经被定义,那么c将被综合为a和b的按位与。如果以后设计需要该为用或门,则将第一行的编译指令改为如下即可:

`define OR

与条件生成语句一样,每次修改后必须重新编译才能生效。

timescale指令

时标指令是用来定义时间单位和时间精度的,它一般用于仿真和时序分析中,语法如下:

`timescale <number0> <unit0> / <number1> <unit1>

- 1

其中 表示在后续程序中,数值每增加1所对应的时间增加量; 表示了小数部分所能描述的精度。为了防止不必要的混淆,Verilog规定的值只能是1、10或者100。举例如下:

`timescale 10ns / 1ns

a = 1'b0; #1; a = 1'b1; #0.5; a = 1'b0; #0.3;

a = 1'b1;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

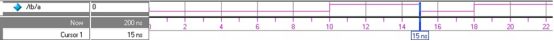

那么上述程序的执行结果如下:

inlcude指令

包含指令对于复杂工程设计来说很有用,有了这个指令,我们就可以在一个文件中定义好工程系统中需要用到的参数、函数、任务等等,然后在需要使用这些资源的的文件中通过include命令将它们包含进来。这种做法非常像C语言中的头文件,因此我们一般都将被include的文件以“*.vh”命名,即verilog header。包含指令的语法如下:

`include "<file_name>"

举例如下:

`include "para.vh"

`include "../data/para.vh"

`include "c:/data/para.vh"

- 1

- 2

- 3

- 4

- 5

上述三条语句分别对应同一目录下的引用,相对路径引用和绝对路径引用。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/104305200

- 点赞

- 收藏

- 关注作者

评论(0)