FPGA之道(75)静态时序分析(一)基本概念介绍

前言

本文来自于《FPGA之道》,一起看作者对于时序分析这一专题的理解。

基本概念介绍

在介绍时序分析之前,让我们先来了解一些相关的基本概念。

常用时间参数介绍

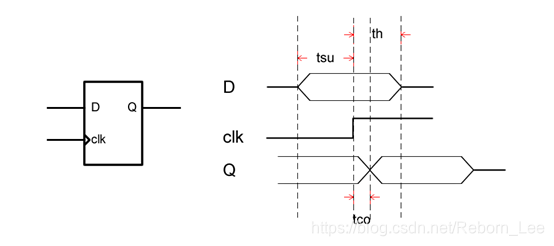

时序分析主要是针对时序逻辑来说的,而时序逻辑中最基本的单元则是寄存器,因此,本章节就让我们围绕下图来谈一谈与寄存器相关的一些重要的时间参数:

tsu

建立时间,英文全称setup time。它是指在有效的时钟边沿信号到来之前,端口D上数据持续稳定不变的时间,如上图中tsu所示。

建立时间要求

建立时间要求,指的就是要想寄存器能够如期的工作,在有效的时钟边沿信号到来之前,D端口上的数据至少需要持续保持稳定不变的时间,也就是寄存器能够正常工作所允许的最小tsu。注意,建立时间要求也可能为零甚至负数,它跟寄存器的类型和具体实现结构有关。

建立时间余量

建立时间余量 = tsu - 建立时间要求。如果建立时间余量大于等于0,则表示寄存器能够正常工作;否则,表示寄存器无法实现预期功能。

th

保持时间,英文全称hold time。与建立时间相对应,保持时间是指在有效的时钟边沿信号到来之后,端口D上数据持续稳定不变的时间,如上图中th所示。

保持时间要求

保持时间要求,指的就是要想寄存器能够如期的工作,在有效的时钟边沿信号到来之后,D端口上的数据至少仍需要持续保持稳定不变的时间,也就是寄存器能够正常工作所允许的最小th。注意,建立时间要求也可能为零甚至负数,它跟寄存器的类型和具体实现结构有关。

保持时间余量

保持时间余量 = th - 保持时间要求。如果保持时间余量大于等于0,则表示寄存器能够正常工作;否则,表示寄存器无法实现预期功能。

tco

时钟至输出延迟,英文全称clock to output delay。当寄存器clk端口的时钟信号与D端口的数据信号的时序关系满足建立时间和保持时间要求时,tco指的就是从时钟有效边沿到达寄存器时开始,到端口Q上稳定得到D端口采样的时间,如上图中tco所示。

Maximum frequency (or Minimum period)

最大时钟频率(或最小时钟周期)。它指的是在确保FPGA设计能够正确实现其功能的前提下,时钟信号所能允许的最大频率(或最小周期)。

线延迟与门延迟

通过【知己知彼篇->组合逻辑电路与时序逻辑电路】、【程序设计篇->编程思路->编写纯净的组合或时序逻辑】等相关章节的介绍,我们了解到,时序逻辑分为以寄存器为代表的存储功能部分和纯组合逻辑部分。其实,时序分析的目的,就是要确保时序逻辑的存储功能部分能够正确的储存我们想要它存储的数据,因此在上一章节中,我们围绕着寄存器,介绍了时序分析相关的一些重要参数。但是,同样的FPGA芯片、同样的寄存器,为什么有时候就能够正确实现数据寄存功能?有时候就不行呢?原因就在于不同时序逻辑中的纯组合逻辑部分大不相同。不同功能或不同实现的组合逻辑,其对应的时间延迟是不同的,因此,组合逻辑的延迟时间求解是时序分析中的重头戏。那么,本章节就来简单介绍一下与组合逻辑相关的时间延迟。

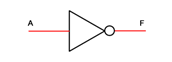

简单来说,组合逻辑的延迟主要取决于两个方面——线延迟和门延迟(其实寄存器等存储单元的相关时间参数和延迟特性,其本质也是线延迟和门延迟,只不过一旦FPGA芯片的具体封装、型号、速度等级确定后,类似寄存器这样存储单元的各项延迟特性就不再改变,因此我们用建立时间要求、保持时间要求、tco等参数来进行总结,并且可以简化其在时序分析时的复杂度)。其中,线延迟指的是连线对电信号造成的传输延迟,这跟连线的阻抗模型、分段寄生电容、电感以及连线长度等等都有很大关系,它取决于FPGA设计最终在芯片内的布局布线情况。而门延迟指的是组合逻辑中所使用的具体门单元电路在进行电信号处理时所带来的延迟,例如,对于下图所示的非门来说,

如果输入端A发生了变化,那么输出端F得到稳定的对应于A端新值的输出所需要的时间便是这个非门的门延迟。FPGA芯片中的各类门延迟跟其底层硬件实现息息相关,而一段组合逻辑的总体门延迟则取决于其设计、综合、转换、映射等环节的工作。

由于线延迟的相关信息要等布局布线工作完成后才能进行评估,而门延迟的相关信息则可以在映射工作完成后得到,因此,就像【开发流程篇->FPGA设计的时序分析】章节中所说的,时序分析可以在两个不同的时间点以不同的方式介入,分别被称为映射后时序分析与布局布线后时序分析。而本章,我们主要关注的则是可信度更高的布局布线后时序分析。

影响延迟的因素

不得不非常遗憾地说一句,即便是布局布线全部完成,我们的FPGA设计已经由确定的FPGA芯片、确定的门电路和确定的物理连线所实现,线延迟、门延迟仍然存在着变数,因为物理电路的特性会受很多因素的影响,而其中最主要的就是温度和电压。

温度与电压

基本RC电路的特性

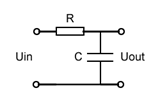

我们先来分析一下如下基本RC电路的充、放电特性:

当Uout初始为逻辑0时,Uin从逻辑0顺便为逻辑1,此时,围绕着电容C展开充电过程。通过模拟电路的一些先验知识,我们可以知道,Uout的增长速度是与电容、电阻的乘积RC成类似反比关系的,即RC越大,Uout的增长速度越慢;反之越快。

而当Uout初始为逻辑1时,Uin从逻辑1瞬变为逻辑0,此时,围绕着电容C展开放电过程。基于同样的先验知识,我们可以知道,Uout的减少速度也是与电容、电阻的乘积RC成类似反比关系的,即RC越大,Uout的减少速度越慢;反之越快。

若RC固定不变,那么,当上述电路充电时,无论Uin的实际电压是多少,Uout从0V增长到kUin(k为大于0小于1的系数)的时间都是一样的;类似的,当上述电路放电时,无论Uout的实际电压是多少,Uout从Uout减少到kUout(k为大于0小于1的系数)的时间也都是一样的。

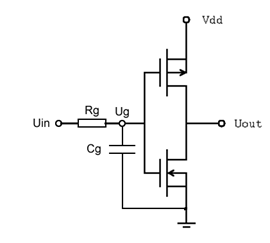

以上便是RC电路的一些基本特性。之所以要介绍RC电路,是因为如果考虑到FPGA内部电路的寄生电容和电阻的话,在忽略掉一些不重要参数后,以反相器为例,在考虑到输入连线的情况下,其对应的CMOS原理电路可近似看成如下所示:

可以看出,该反相器的输入端此时就相当于一个RC电路,而其主要功能是由一个PMOS和一个NMOS串联而成,下面,便以此电路为例,简要介绍温度、电压对延迟的影响。

温度对延迟的影响

简单来说,温度越高,分子的热运动就会越剧烈,从而更容易阻碍电子在导体、半导体内部的运动,而其最显著的影响就是使得电阻变大。对应到上一小节中的反相器电路,最显著的就是Rg变大,从而RgCg变大。那么,在假设Vdd此时保持不变的前提下,进行分析如下:

让我们先来分析一下温度增加前后,以Uin从逻辑0翻转到逻辑1开始,到Uout从逻辑1变为逻辑0结束的时间长度变化。首先,Uout从逻辑1变为逻辑0的响应速度,主要取决于电路下方NMOS导通的快慢,而NMOS导通的条件是Ug≥V_TN。由于温度升高后,RgCg变大,从而Ug从0V增加到V_TN所需的时间变长,因此也会最终导致Uout经过较长时间才能变为逻辑0。

采用类似的分析思路,对Uin从逻辑1翻转到逻辑0开始,到Uout从逻辑0变为逻辑1结束的时间长度变化进行分析。首先,Uout从逻辑0变为逻辑1的响应速度,主要取决于电路上方PMOS导通的快慢,而PMOS的导通条件是Ug≤〖Vdd-V〗_TP。由于温度升高后,RgCg变大,从而Ug从Vdd减少到〖Vdd-V〗_TP所需的时间变长,因此也会最终导致Uout经过较长时间才能变为逻辑1。

经过以上粗略的分析,可以推出一个结论,温度越高各类延迟也就越大(事实上是随着温度的升高,延迟至少不会减少)。因此,我们要尽可能的抑制FPGA芯片在工作时候的温度升高,最显著的手段就是为FPGA芯片增加散热片。

电压对延迟的影响

仍以【基本RC电路的特性】小节中的反相器电路为例,来简单分析一下电压的升高对延迟的影响,此时,假设温度一直保持不变,从而Rg不变,RgCg不变,分析如下:

让我们先来分析一下Vdd增加前后,以Uin从逻辑0翻转到逻辑1开始,到Uout从逻辑1变为逻辑0结束的时间长度变化。首先,Uout从逻辑1变为逻辑0的响应速度,主要取决于电路下方NMOS导通的快慢,而NMOS导通的条件是Ug≥V_TN。由于Vdd升高后,对电容Cg充电的电流也等比变大,从而Ug从0V增加到V_TN所需的时间变短,因此也会最终导致Uout经过较短的时间就能变为逻辑0。

采用类似的分析思路,对Uin从逻辑1翻转到逻辑0开始,到Uout从逻辑0变为逻辑1结束的时间长度变化进行分析。首先,Uout从逻辑0变为逻辑1的响应速度,主要取决于电路上方PMOS导通的快慢,而PMOS的导通条件是Ug≤〖Vdd-V〗_TP。无论Vdd为何值,电容Cg的放电量都只需达到CgV_TP即可保证PMOS导通,由于Vdd升高后会导致Ug升高,故电容的放电电流也会等比增加,所以Ug从Vdd减少到〖Vdd-V〗_TP所需的时间变短,因此也会最终导致Uout经过较短时间就能变为逻辑1。

经过以上粗略的分析,可以推出一个结论,电压越高各类延迟会变得越小(事实上是随着电压的升高,延迟至少不会增加)。不过,我们并不推荐让Vdd取到允许范围内的最大值,因为电压越高,功耗越大,从而也会引起温度的升高,并且电压太高也会让器件承担过重,减少器件的寿命,所以电压方面通常就是按照手册上推荐的供电取值即可。

三种工况

基于【温度与电压】章节中的讨论,针对FPGA的时序分析通常会针对三种不同的温度、电压组合情况来展开,而这三种不同的组合情况又称为时序分析时的三种工况,即——最大工况、最小工况和典型工况。

其中,最大工况是温度取允许范围内的最大值、电压取允许范围内的最小值,编译器以此条件为依据,给出布局布线后的各个门延迟和线延迟参数,供时序分析工具进行分析。由于此时为延迟最大的极限情况,故最大工况主要关注FPGA设计在实现时,各个寄存器的建立时间是否满足极限要求,从而可以确定出各个时钟信号所能够允许的最大工作频率。

最小工况的情况则是温度取允许范围内的最小值、电压取允许范围内的最大值。由于此时为延迟最小的极限情况,故最小工况主要是关注各个寄存器的保持时间是否满足极限要求。

而典型工况的情况则是温度取常温(通常为25摄氏度)、电压取手册推荐值。此时对建立和保持时间的要求都比较适中,是较为常见的工作情况,主要用于分析普通情况下寄存器是否能够正常工作。

时钟信号的偏差描述

一个理想的时钟应该具有一个稳定的周期T(稳定的频率f),但是,现实中的时钟信号都不可能是十分理想的,它总存在着或多或少的偏差,而这些偏差也对时序分析有着非常重要的影响。因此,本章节我们就来简单了解一下几个常见的跟时钟信号偏差相关的概念。

时钟精度

如果我们需要一个频率为f0的时钟信号,可是实际中电路给出的是一个频率为f1的时钟信号,那么∆f=|f0 -f1|,就是理想和实际的误差,而∆f与f0的比值,则可以用来表示时钟信号的精确程度。

时钟漂移

如果我们需要一个频率为f0的时钟信号,但实际中电路给出的是一个频率围绕f0不断变化的时钟信号,例如,fl < f0 < fh,实际电路所给出的时钟信号频率总是在f1与f2之间过渡变化。这种时钟信号频率的长期可观测变化就叫做时钟漂移。

jitter

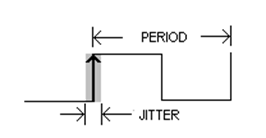

jitter是时钟抖动的意思,它指的是相比时钟漂移更短期的时钟抖动。如果我们的时序逻辑是由时钟信号的上升沿驱动的,那么我们所关注的jitter就是针对上升沿来说的,如下图所示:

可见,jitter描述了时钟信号有效边沿到来的一种周期内不确定性,即,如果时钟信号的周期为T,0时刻对应第一个上升沿,那么当时钟信号非常理想的时候,其上升沿应该依次出现在T、2T、3T、……、NT、……时刻。可是,由于电路各部分器件的热噪声、晶振本身的抖动等等原因,现实中时钟上升沿的到来时刻往往会和整数倍T时刻有一定偏差,但是只要第N+1个上升沿总是会在NT时刻的附近到来,并且其与NT时刻的偏差总是存在着一定随机性,那么这种偏差就叫时钟的jitter。

skew

skew是时钟歪斜,也叫时钟脉冲相位差。它指的是由于时钟信号到达各个寄存器的路径不同,因此对于同一个时钟有效边沿,有的寄存器处到来的早,而有的寄存器处到来的晚,这样一来,同一个时钟信号到达各个寄存器的时间便不一致。那么,这种时间上的偏差就叫做clock skew。

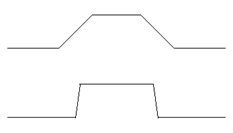

slew rate

slew rate,简写为SR,是电压转换速率的意思,简称压摆率,其常用单位有V/s,V/ms,V/us和V/ns四种。可见,压摆率越大,时钟信号完成0、1转换的速度也就越快,转换斜率也就越大。下图形象的描述了低压摆率与高压摆率的时钟信号区别:

显然,我们更希望能够得到压摆率更高的时钟信号,不过压摆率越高,时钟信号的频谱也就越宽,受限于实际的传输介质,高频一些的时钟信号往往都程现出正弦波形的特性。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/105083419

- 点赞

- 收藏

- 关注作者

评论(0)