FPGA设计心得(3)Aurora IP core 的理论学习记录

Aurora IP核介绍

整体介绍

FPGA之间通过Aurora 8B/10B IP核进行通信的示意图如下:

通信的双方经过各自例化IP核,通过通道传输数据,用户能够操作的是User Application以及IP的定制。

通信的双方经过各自例化IP核,通过通道传输数据,用户能够操作的是User Application以及IP的定制。

使用Aurora IP核通信,更详细的方框图如下:

方框内为IP核的东西,可以选择通道的数量:

方框内为IP核的东西,可以选择通道的数量:

可以想象在FPGA的芯片上,一个型号的芯片上有多少个mgt bank,一个bank上有几个通道,以封装为ffg900的k7325t为例:

可以想象在FPGA的芯片上,一个型号的芯片上有多少个mgt bank,一个bank上有几个通道,以封装为ffg900的k7325t为例:

有4个MGTbank,每个bank上有4个通道(channel),在Aurora中就叫做lane了。

有4个MGTbank,每个bank上有4个通道(channel),在Aurora中就叫做lane了。

下图是更详细的结构:

每一个MGT bank的四个通道加上一个GTXE2_COMMON时钟原语构成一个QUAD。

不再细究!

从这此图的接口方向也不难看出:

用户操作的逻辑在IP核之外,我们需要处理IP核接收的数据以及根据自己的需求发送数据到IP核进行通信。

用户操作的逻辑在IP核之外,我们需要处理IP核接收的数据以及根据自己的需求发送数据到IP核进行通信。

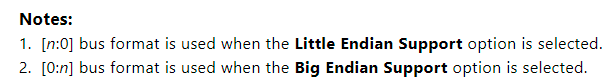

大小端

在IP核的定制中,有一个大小端的选择问题:

所谓的小端,就是我们最常见的多位数据定义方式:

[n:0] 左边是高位,右边是低位,符合Verilog编写习惯,大端反之。

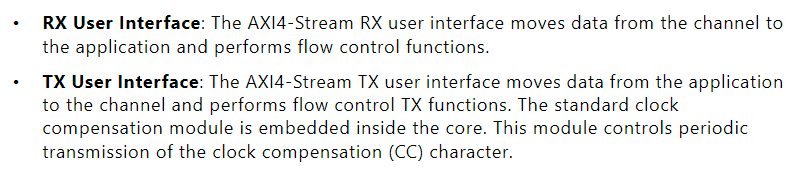

Framing or Streaming User Interface

在定制IP核过程中,有用户接口这一个选择:

有两种选择,Framing和Streaming用户接口,至于如何清晰地使用这两种接口,这里也说不清,但能肯定地是Streaming格式更加容易上手,如下描述:

The framing user interface complies with the AMBA® AXI4-Stream Protocol Specification [Ref 4] and comprises the signals necessary for transmitting and receiving framed user data. The streaming interface allows data to be sent without frame delimiters, is simpler to operate, and uses fewer resources than a framing interface.

framing 接口介绍

关于framing用户接口,数据手册有详细介绍:P14

接口框图:

接口框图:

发送数据以及接受数据时,

发送数据以及接受数据时,

To transmit data, the user application manipulates control signals to cause the core to do the following:

• Take data from the user interface on the s_axi_tx_tdata bus when s_axi_tx_tvalid and s_axi_tx_tready signals are asserted.

• Stripe the data across lanes in the Aurora 8B/10B channel.

•Use the s_axi_tx_tvalid signal to transmit data. The user application can deassert s_axi_tx_tvalid to insert idles on the line (introduce stalls or pause).

• Pause data (that is, insert idles) (s_axi_tx_tvalid is deasserted).

发送数据,用户应用程序操纵控制信号以使内核执行以下操作:

•当s_axi_tx_tvalid和s_axi_tx_tready信号有效时,从s_axi_tx_tdata总线上的用户接口获取数据。

•在Aurora 8B / 10B通道中的通道之间划分数据。

•使用s_axi_tx_tvalid信号传输数据。 用户应用程序可以将s_axi_tx_tvalid置为无效以在该行上插入空闲字符(导致停顿或暂停)。

•暂停数据(即插入空闲)(s_axi_tx_tvalid置为无效)。

接受数据时:

When the core receives data, it does the following:

• Detects and discards control bytes (idles, clock compensation, Start of Channel PDU (SCP), End of Channel Protocol Data Unit (ECPDU) and PAD.

• Asserts framing signal (m_axi_rx_tlast) and specifies the number of valid bytes in the last data beat (m_axi_rx_tkeep).

• Recovers data from the lanes

• Assembles data for presentation to the user interface on the m_axi_rx_tdata bus by asserting of the m_axi_rx_tvalid signal.

翻译过来:

当核心接收数据时,它将执行以下操作:

•检测并丢弃控制字节(空闲,时钟补偿,通道PDU(SCP)的开始,通道协议数据单元(ECPDU)的结束和PAD。

•置位成帧信号(m_axi_rx_tlast),并指定最后一个数据拍子(m_axi_rx_tkeep)中的有效字节数。

•从通道中恢复数据

•通过置位m_axi_rx_tvalid信号来组装数据,以呈现给m_axi_rx_tdata总线上的用户接口。

注意:

仅当同时声明s_axi_tx_tready和s_axi_tx_tvalid时,Aurora 8B / 10B内核才对数据采样(高)。

AXI4-Stream data is only valid when it is framed. Data outside of a frame is ignored.

To start a frame, assert s_axi_tx_tvalid while the first word of data is on the s_axi_tx_tdataport. To end a frame, assert s_axi_tx_tlast while the last word (or partial word) of data is on the s_axi_tx_tdata port and use s_axi_tx_tkeep to specify the number of valid bytes in the last data beat.

AXI4-Stream数据仅在帧内时才有效。 帧外的数据将被忽略。 要开始帧,请在数据的第一个字位于s_axi_tx_tdataport上时有效s_axi_tx_tvalid。 要结束帧,请在数据的最后一个字(或部分字)位于s_axi_tx_tdata端口上时有效s_axi_tx_tlast,并使用s_axi_tx_tkeep指定最后一个数据拍中的有效字节数。

如果帧的长度不超过一个字,则同时使s_axi_tx_tvalid和s_axi_tx_tlast有效。

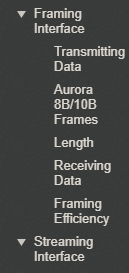

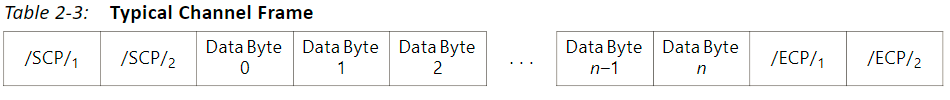

framing 结构

典型的framing结构如下:

TX子模块通过TX接口将每个接收到的用户帧转换为Aurora 8B / 10B帧。 通过在帧的开头添加一个2字节的SCP代码组来指示帧的开始(SOF)。 帧的结尾(EOF)通过在帧的末尾添加2字节的通道结束协议(ECP)代码组来表示。 只要没有数据,就会插入空闲代码组。 代码组是8B / 10B编码的字节对,所有数据都作为代码组发送,因此具有奇数字节的用户帧在帧末尾附加了一个称为PAD的控制字符,以填充最终的代码组。

用户应用程序通过操纵s_axi_tx_tvalid和s_axi_tx_tlast信号来控制通道帧长度。 Aurora 8B / 10B核分别响应帧开始和帧结束有序集/ SCP /和/ ECP /。

来源:数据手册P15

几个frame的例子

有关发送以及接受frame结构数据的例子将会令外立博文解释,下面给出波形图 预告:

情况1:无中断传输偶数个字节数据

情况2:无中断传输奇数个字节数据(填充字节PAD)

情况3:有中断传输数据

情况4:传输具有时钟补偿的数据

更新了会附上链接。

streaming接口介绍

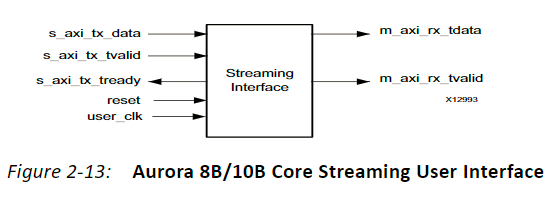

streaming用户接口示意图如下:

与framing用户接口对比,如下:

可见,相比于framing用户接口,Streaming用户接口简洁很多。

发送端仅有三个信号,接收端两个:

流接口允许将Aurora 8B / 10B通道用作管道。 初始化之后,该通道始终可用于写入,但发送时钟补偿序列时除外。 核心数据传输符合AXI4-Stream协议。

当s_axi_tx_tvalid置为无效时,字之间会创建间隙并保留间隙,除非正在发送时钟补偿序列。

当数据到达Aurora 8B / 10B通道的RX端时,它会显示在m_axi_rx_tdata总线上,并且会使m_axi_rx_tvalid有效。 数据必须立即读取或丢失。 如果不可接受,则必须在RX接口上连接一个缓冲区以保存数据,直到可以使用为止。

Streaming接口发送数据实例

Aurora 8B / 10B核通过置位s_axi_tx_tready表示已准备好传输数据。 一个周期之后,用户逻辑通过置位s_axi_tx_tdata总线和s_axi_tx_tvalid信号来表明已准备好传输数据。

因为现在两个就绪信号都被声明,所以数据D0从用户逻辑传输到Aurora 8B / 10B核。 数据D1在下一个时钟周期传输。

在此示例中,Aurora 8B / 10B核将其就绪信号s_axi_tx_tready置为无效,并且直到下一个时钟周期再次置位s_axi_tx_tready信号时,才传输下一个数据。 然后,用户逻辑在下一个时钟周期将s_axi_tx_tvalid置为无效,直到两个就绪信号都被置为有效,才传输下一个数据。

streaming接口接受数据实例

很简单,只要valid信号有效,则tdata数据总线上数据为有效数据。

写在最后

下一篇博文讲一下IP核的定制细节。

同行邀请

参考资料

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/106057834

- 点赞

- 收藏

- 关注作者

评论(0)