固态器件理论(5)PN结

写在前面

原文链接

相关博文

博客首页

注:知识搬运,供学习交流使用,侵联删!

正文

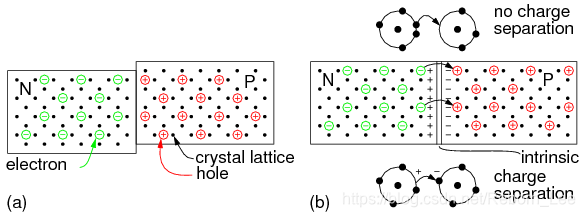

如果将一块P型半导体块与下图(a)中的N型半导体块接触,则结果将没有价值。我们有两个相互接触的导电块,没有表现出独特的性能。问题是两个单独且不同的晶体。两个晶体块中的电子的数量与质子的数量相同。因此,两个块都没有任何净电荷。

但是,在下图(b)中,一端为P型材料而另一端为N型材料制成的单个半导体晶体具有一些独特的性能。 P型材料具有正多数电荷载流子,空穴,它们可自由围绕晶格移动。 N型材料具有可移动的负多数载流子电子。在结附近,N型材料电子扩散穿过结,并与P型材料中的空穴结合。由于吸引了电子,结附近的P型材料区域带净负电荷。由于电子离开了N型区域,因此它具有局部正电荷。这些电荷之间的晶格薄层已经耗尽了多数载流子,因此被称为耗尽区。成为非导电本征半导体材料。实际上,我们几乎有一个绝缘体将导电的P和N掺杂区分开。

(a)接触的P和N半导体块没有可利用的特性。 (b)掺有P和N型杂质的单晶形成势垒。

PN结处的电荷分离构成了势垒。 必须通过外部电压源克服该势垒,以使结导通。 结和势垒的形成发生在制造过程中。 势垒的大小取决于制造中使用的材料。 硅PN结具有比锗结更高的势垒。

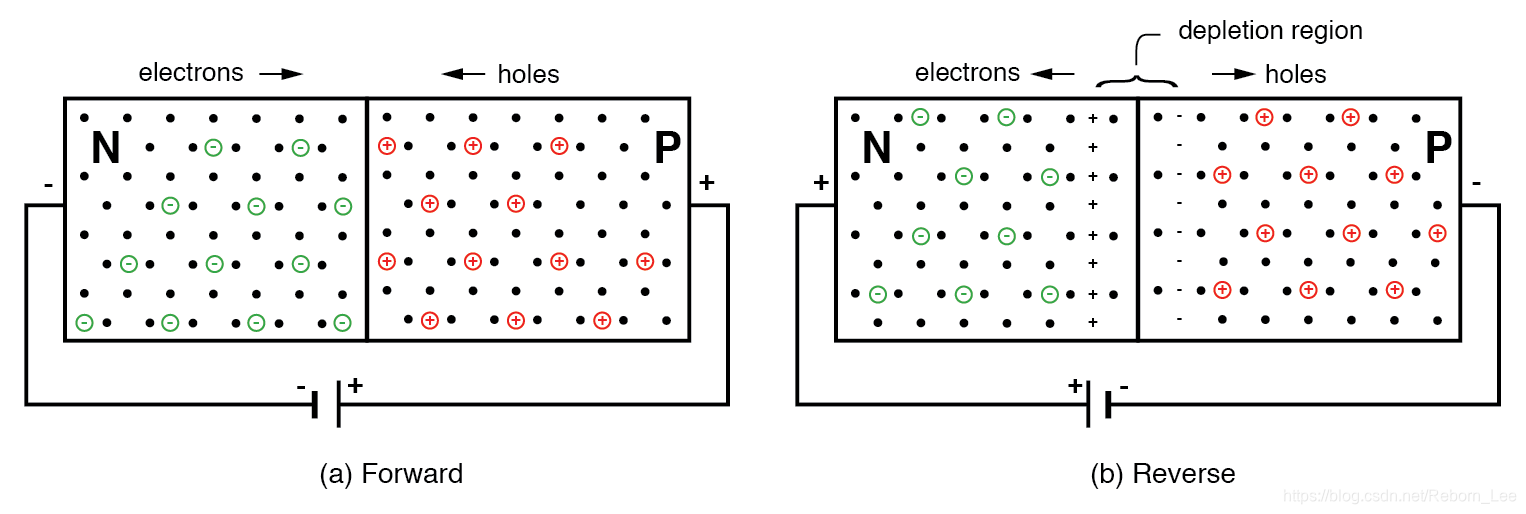

PN结偏置

在下图(a)中,电池的排列方式是使负极端子将电子提供给N型材料。 这些电子向结扩散。 正极端子将电子从P型半导体中移除,从而产生向结扩散的空穴。 如果电池电压足够大以克服结电势(Si中为0.6V),则N型电子和P型空穴会相互抵消。 这释放了晶格内的空间,使更多的载流子流向结。 因此,N型和P型多数载流子的电流流向结。 结点的重组使电池电流流过PN结二极管。 这种结点被称为前向偏置的。

如果电池极性如上图(b)所示相反,则多数载流子会从结点吸引到电池端子。 电池正极端子从结处吸引N型多数载流子电子。 负极端子从连接处吸引P型多数载流子,空穴。 这增加了非导电耗尽区的厚度。 没有多数载体的重组; 因此,没有传导。 电池极性的这种排列称为反向偏置。

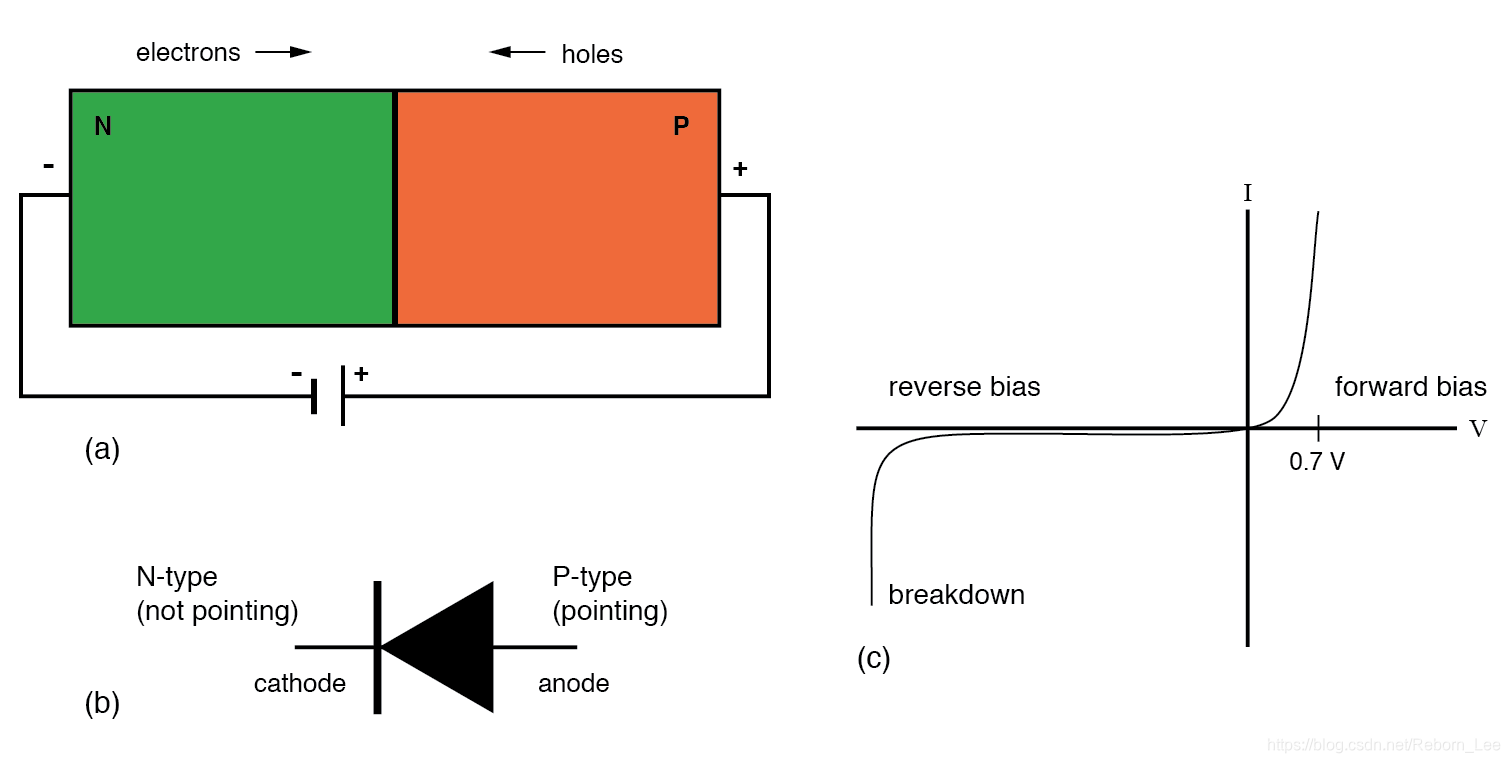

二极管

二极管的示意图符号在下面的图(b)中对应于(a)中的掺杂半导体条。 二极管是单向器件。 电流仅沿一个方向流动,沿着箭头,对应于正向偏置。 二极管符号的阴极bar对应于N型半导体。 阳极箭头对应于P型半导体。 为了记住这种关系,符号上的未指向(条形)对应于N型半导体。 指向(箭头)对应于P型。

(a)正向偏置PN结,(b)相应的二极管示意图符号(c)硅二极管的I与V特性曲线。

如果二极管如上图(a)所示被正向偏置,则电流会随着电压从0 V的增加而略有增加。对于硅二极管,当上图中的电压接近0.6 V时,可测量的电流会流过)。当电压增加到超过0.6 V时,拐点后电流会大大增加。将电压增加到超过0.7 V可能会导致足够高的电流以破坏二极管。正向电压VF是半导体的特性:硅为0.6至0.7 V,锗为0.2 V,发光二极管(LED)为几伏。正向电流范围从点接触二极管的几mA到小信号二极管的100 mA到功率二极管的数十或数千安培不等。

如果二极管反向偏置,则仅本征半导体的泄漏电流流动。在上图(c)中将其绘制在原点的左侧。对于硅小信号二极管的最极端条件,该电流仅会高达1 µA。直到二极管击穿,该电流才不会随着反向偏置的增加而明显增加。击穿时,电流会大大增加,除非高串联电阻限制电流,否则二极管将被破坏。通常,我们选择反向额定电压高于任何施加电压的二极管来防止这种情况。硅二极管通常具有50、100、200、400、800 V和更高的反向击穿额定值。可以制造几伏的较低额定值的二极管作为电压标准。

前面我们曾提到,硅二极管的反向泄漏电流低于µA,这是由于本征半导体的导电引起的。 这是可以用理论解释的泄漏。 热能产生很少的电子-空穴对,它们传导泄漏电流直到复合。 在实际中,这种可预测的电流只是泄漏电流的一部分。 大部分泄漏电流归因于表面传导,这与缺乏半导体表面的清洁度有关。 两种泄漏电流都随着温度的升高而增加,对于小型硅二极管,其泄漏电流接近µA。

对于锗,泄漏电流要高几个数量级。 由于锗半导体目前很少使用,因此在实践中这不是问题。

回顾

PN结是由单晶半导体制成的,在结附近有一个P型和N型区域。

电子从结的N侧传输到在结的P侧抵消空穴,产生势垒电压。 在硅中为0.6至0.7 V,并且随其他半导体而变化。

一旦克服了势垒电压,正向偏置的PN结就会传导电流。 外部施加的电势迫使多数载流子流向发生重组的结,从而允许电流流动。

反向偏置的PN结几乎不传导电流。 施加的反向偏置将多数载流子从结吸引开。 这增加了非导电耗尽区的厚度。

反向偏置的PN结显示出与温度有关的反向泄漏电流。 在小型硅二极管中,该电流小于µA。

交个朋友

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/106433611

- 点赞

- 收藏

- 关注作者

评论(0)