FPGA设计心得(11)关于FIFO IP核使用的一点注意事项

前言

FIFO? 还是FIFO IP核?这也需要写总结吗?太容易了吧。

如果我是一个正在处于面试找工作中的年轻人,肯定关注的是如何手撕FIFO,这也是当时校招时候干过的事情。

但是作为一个FPGA工程师,我们更常使用的是FIFO的IP核,或者必然使用的是FIFO IP核,简单快捷优化。

使用FIFO IP核的时候,或者设计电路使用FIFO IP的时候,对于新手或者不是精通的情况下,个人建议一点是对自己定制的FIFO仿真一下(或者严格遵守数据手册),做到时序关系清晰后,再设计电路。

注意:不要不屑于此!

下面讲解几点关于FIFO IP核使用时的注意事项,想到哪里到哪里!

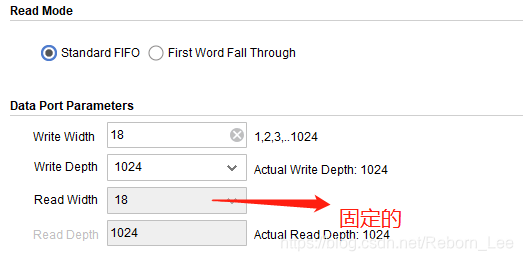

位宽转换

分布式ram资源的FIFO不能变换位宽

Block RAM资源可以变化位宽

Builtin FIFO资源不能变化位宽

FIFO 安全电路

FIFO定制页面存在一个Enable Safety Circuit,如下:

选择此选项,存在两个额外输出信号:

如果不选择Enable Safety Circuit,则不存在这两个信号输出:

此选项仅仅针对基于Bram资源的FIFO定制,如果使用分布式RAM资源,则不可选择:

同理Builtin FIFO资源的FIFO也不可选择。

假如使用的是此Block RAM资源的FIFO,选择此信号,有什么作用呢?

多出来的两个信号是什么意思?有什么用途?

笔者曾在仿真中犯过一个错误,就是在复位后的几个时钟直接给写使能,可是怎么写也写不进去数据,后来发现是wr_rst_busy处于高电平状态,自然是不能写的。

所以判断写使能有效,可以将此信号作为判断条件之一,如果该信号为高,则不能写入。

这就引发一个疑问?既然存在这样一个问题,那么多久之后才能对FIFO写入数据呢?

那就要看复位无效之后多久这个信号才能被拉低,且仿真看看:

可见,大概20多个时钟周期之后,这个信号就拉低无效了。

这样会不会对我们使用FIFO有影响呢?

可以想象下20多个时钟才多长时间,周期ns级别,况且写使能可以以此信号作为写使能有效条件,因此可以很容易规避这个问题,这里列出来的原因就是为了仿真时候,如果遇到了写不进去的情况时,考虑下这个问题,以免莫名其妙,百思不得其解。

Xilinx对安全电路的使用还有一条建议,就是选择异步复位时,有可能导致BRAM数据的损坏,此时推荐使用安全电路。

对于异步FIFO而言,好像也只能使用异步复位,这就更有必要性了。

FIFO消耗资源

定制FIFO消耗资源与使用什么资源生成FIFO有关,对于Block RAM资源的FIFO使用的自然是Block RAM资源,7系列的用于生成FIFO的Block RAM资源大小有两种,18Kbit以及36Kbit两种,一般默认bit,可以说是18K以及36K。

FIFO位宽乘深度小于18K,自然是使用了一个18K的Bram,如下:

使用Block RAM资源:

大于18K的自然是一个36KBlock RAM:

使用BRAM资源:

大于36K,情况多变,是18K以及36K的组合:

输出延迟

Read Latency为1的含义

使用分布式RAM资源以及Block RAM资源的FIFO可以选择输出寄存器打拍一次,这样自然Read Latency为2,使用Builtin FIFO资源无法选择输出寄存器打拍。

假如都不寄存器输出,即输出不寄存一拍,那么这里的Read Latency = 1具体是什么含义呢?

我想时序图最能说明一切:

实际仿真看一下:

FIFO IP生成总结:

因此如果需要使用rd_data数据的话,需要对读使能延迟一拍,判断rd_en_r1有效时使用读数据的实际值:

Read Latency为2的含义

知道了Read Latency为1的含义,为2的情况自然很容易理解,在添加了寄存器输出的时候,就会使得Read Latency为2,如下:

同样仿真实现下:

FIFO 读写计数器的含义

在FIFO定制页面有如下选择:

Write Data Count,Read Data Count这两个选择,是什么意思呢?

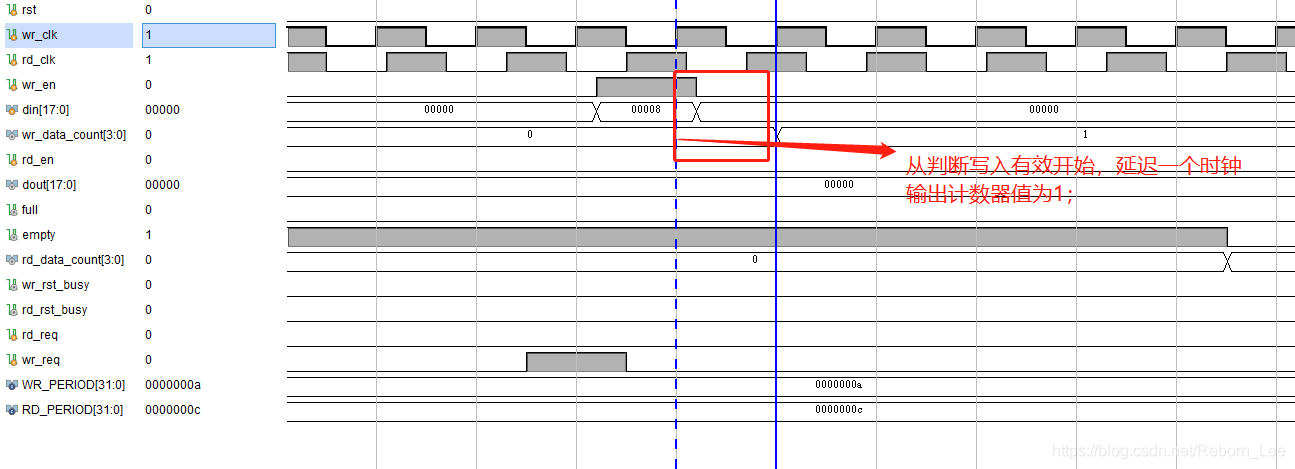

那我们写进去一个数据,看看两者数据的变化:

写计数器

从写计数有效开始,延迟一个时钟,计数器值更新为1,意思就是写入了一个数据;

注意:我们在实际使用FIFO输出参数之前,一定要仿真看下时序关系,以防用错。

我们尝试写入两个数据,来验证下这种关系:

关系一致。

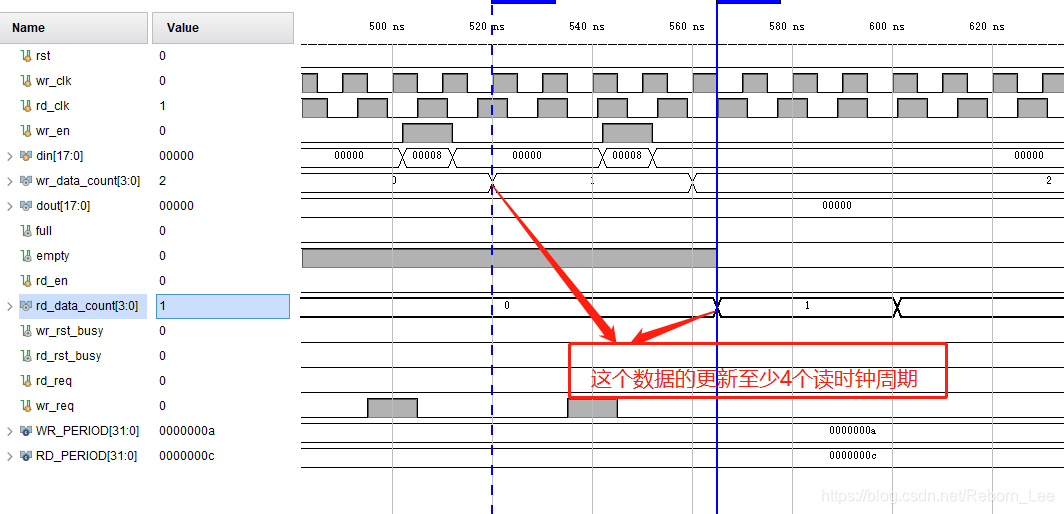

读计数器

读计数器的含义是FIFO内部存放了多少数据?

但这个数据的更新需要一定的时间,例如:

数据的更新需要至少4个读时钟周期,因此,这个数据我们不能写入之后立即使用;

这个延迟是异步FIFO内部跨时钟域的结果。

注意:使用FIFO IP核内部输出信号的时候,保险起见,需要自己仿真下,认识下时序关系后再设计电路。

例如写入了两个数据,之后又读出了一个,那这个值最终一定是1;

仿真验证了这个结果。

上面说了这些情况,其实都在数据手册中有体现,但是对于一个FIFO,大家都倾向于直接使用,不屑于看数据手册,不得不说,这都是年轻气盛的表现,或者天赋异禀。

因此,对于这种情况,我们有两个选择:

一是看数据手册;

二是自己仿真自己定制的IP核,看清时序后设计电路。

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/108553930

- 点赞

- 收藏

- 关注作者

评论(0)