FPGA的设计艺术(4)STA实战之不同时序路径的建立保持时间计算

前言

本文首发:FPGA的设计艺术(4)STA实战之不同时序路径的建立保持时间计算

STA定义

STA定义为:时序验证,可确保各种电路时序是否满足各种时序要求。

ASIC / FPGA设计流程中最重要和最具挑战性的方面之一是时序收敛。时序收敛可以看作是数字电路的时序验证。为时序而闭合的数字电路将以指定的频率工作(由设计人员在时序约束中定义),因此可以实现预期的PPA(性能,功率和面积)。静态时序分析是一种方法,通过该方法,可以通过对数字电路中的所有路径进行时序分析来确定是否实现时序收敛。顾名思义,这种对数字电路的验证是静态完成的(不需要对数字逻辑进行仿真)。静态时序分析利用了数字电路所有起点和终点之间的时序弧(由技术库定义)。必须意识到,由于不涉及仿真,因此静态时序分析将不会检查功能的正确性,而只会关注时序。

STA术语

在深入研究静态时序分析的工作原理之前,获得一些稍后使用的术语的基础知识非常有价值。

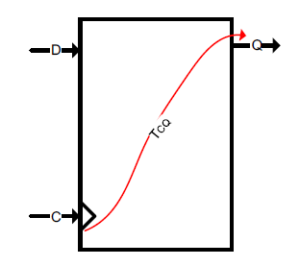

- 时序弧:定时弧是在技术库中为每个单元(cell)定义的参数,这些参数定义了单元在不同PVT拐角处的延迟。静态时序分析使用这些参数来计算通过任何库单元的最大和最小延迟。例如,对于D型触发器,技术库将包含定义建立时间,保持时间和C(时钟)至Q(输出)时间(TCQ)的参数。

TCQ:TCQ定义为一旦触发时钟C(正沿或负沿)数据出现在输出Q上所花费的时间。

建立时间:定义输入D在时钟C触发之前必须稳定的时间(上升沿或下降沿)定义为建立时间。 如果数据至少在时钟沿之前的建立时间之前不稳定,则输出将不确定。

保持时间:触发时钟C后(上升沿或下降沿)输入D必须保持稳定的时间。 如果数据至少在时钟沿之后的保持时间内不稳定,则不确定输出。

静态时序分析可以在设计的时序部分和组合部分中进行。 在任何时序设计路径中,总会有一个发射触发器(驱动数据)和一个锁存触发器(捕获数据)。 通过假设一个虚拟时钟驱动一个虚拟发射或虚拟锁存,也可以将组合路径视为时序路径。

建立时间约束:任何数字电路的建立时间约束都定义为时序约束,因此设计中最慢的路径必须满足锁存触发器的建立时间。

保持时间约束:将任何数字电路的保持时间约束定义为时序约束,以便设计中最快的路径必须满足锁存触发器的保持时间。

如果设计同时满足建立和保持约束,则称该设计已实现时序收敛。 静态时序分析将通过分析设计中的所有时序路径来证明建立和保持时间约束。

STA路径介绍

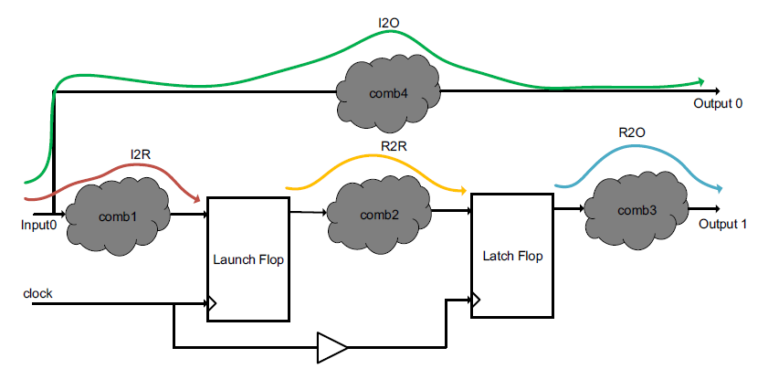

任何数字设计均可分为静态时序分析的四类路径。

- 输入到输出(I2O)

- 输入到寄存器(I2R)

- 寄存器到寄存器(R2R)

- 寄存器到输出(R2O)

在所有这些路径上一一完成静态时序分析。 通过定义该路径的起点和终点来分别分析每个路径。

R2R

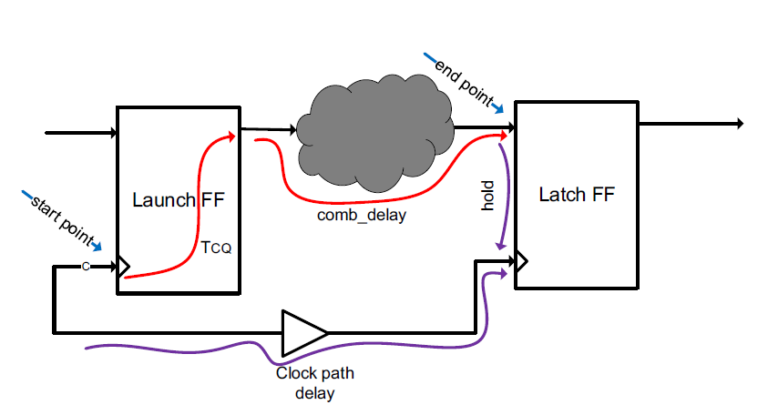

让我们首先考虑R2R路径的静态时序分析。 它们很简单,并成为其他途径的基础。

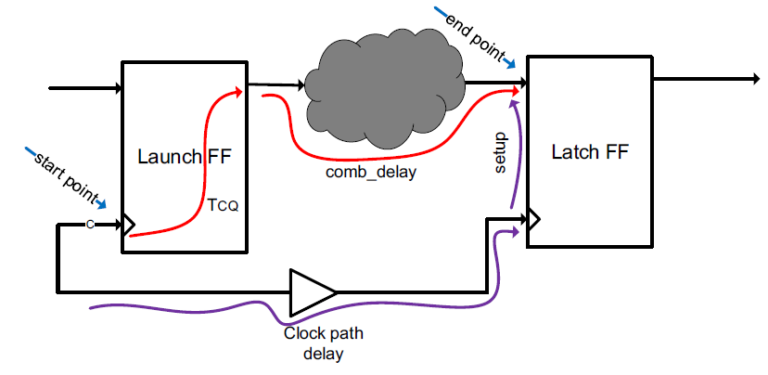

setup计算

对于R2R路径,起点是启动触发器的时钟输入引脚,终点是捕获触发器的D输入引脚。 对于建立时间约束,目标是确保从起点到终点的延迟至少是寄存器的建立时间小于寄存器时钟的时钟周期。 这意味着

TCQ + comb_delay(max)<时钟延迟路径(时钟偏斜)+ T(时钟的时钟周期)– Latch FF的建立时间

- 1

下图中的comb_delay应该是通过组合逻辑的最大延迟。

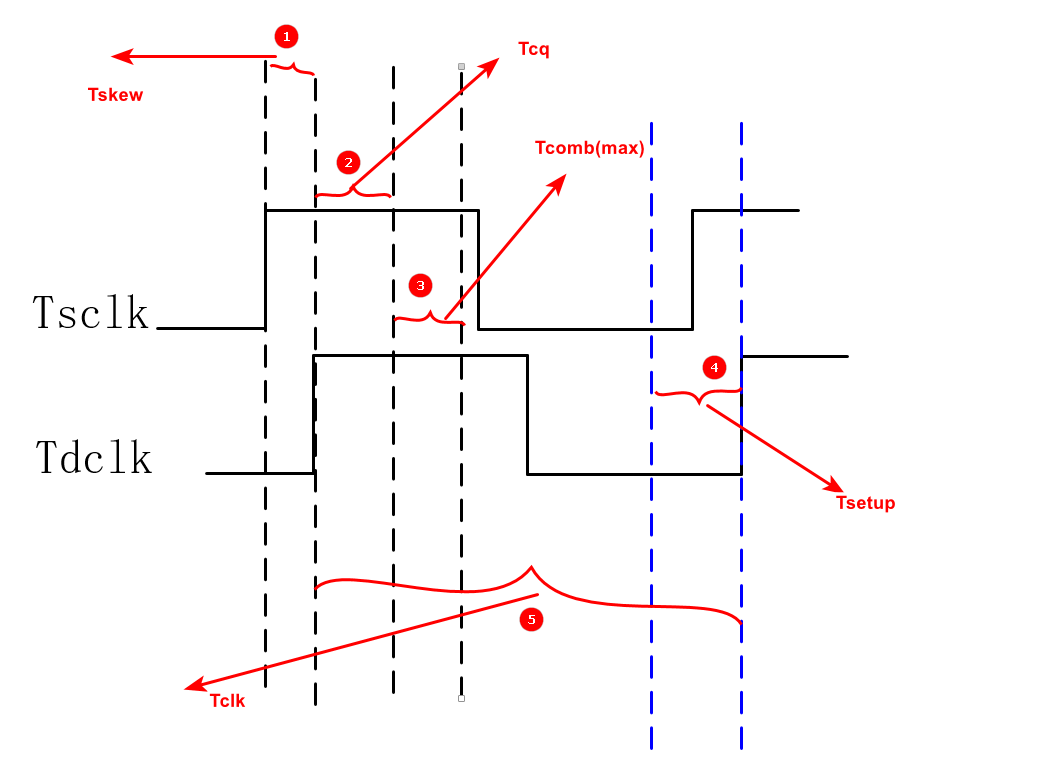

为了有助于理解上述公式,我们给出时序图:

该公式:

TCQ + comb_delay(max)<时钟延迟路径(时钟偏斜)+ T(时钟的时钟周期)– Latch FF的建立时间

- 1

根据上图参数可以改写为:

Tcq + Tcomb(max)+ Tsetup <Tskew+ Tclk 继续改写 Tcq + Tcomb(max)<Tskew+ Tclk - Tsetup

- 1

为什么要满足这样的关系呢?

建立时间的定义简单来说,就是时钟有效沿到达之前数据必须保持稳定的时间。

数据在什么时候就应该到达呢?在 Tcq + Tcomb(max)时就到达了。那么在这个时间之前,捕获寄存器就应该捕获到稳定的数据了。

根据上图可知,数据周期必须满足条件是:Tskew+ Tclk - Tsetup大于 Tcq + Tcomb(max)。

我继续自问几个不太聪明的问题:

为什么要减去Tsetup?

- 因为这是时钟周期需要预留的裕量。

为什么Tcomb要取最大延迟路径?

- 因为最大的延迟路径都满足了,其他延迟路径的建立时间也一定能满足。

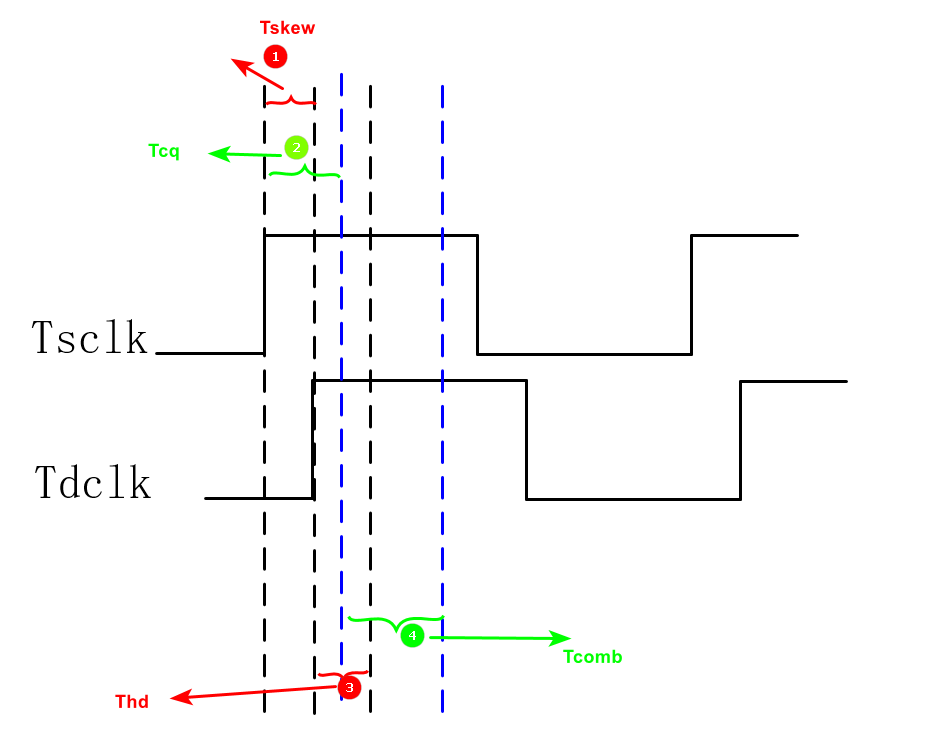

hold计算

对于保持约束,目标是确保通过起点和终点的延迟至少大于相同时钟周期中锁存器的保持时间。

TCQ + comb_delay(min)>锁存器FF的保持时间+时钟延迟路径(时钟偏斜)。

- 1

下图中的comb_delay应该是通过组合逻辑的最小延迟。 可以看到,保持时间不取决于时钟的时钟周期。

如下,需满足保持时间的几个时间参数如下图示意:

上面说需要满足:

TCQ + comb_delay(min)>锁存器FF的保持时间+时钟延迟路径(时钟偏斜)。

- 1

换成上面的图中参数为:

Tcq + Tcomb > Thd + Tskew

- 1

这是为什么呢?

通俗地理解,可以这样解释:

首先解释为什么分析目的时钟(捕获时钟)以及源时钟(发射时钟)的同一个沿?

根据保持时间的定义可知,保持时间就是数据在时钟到达之后需要保持稳定的最大时间。数据达到触发器(或其他时序单元)保持稳定的时间在Tcq(时钟有效沿到数据有效的时间)加组合逻辑延迟以及布线延迟总和之内,在这个时间内为了不让捕获时钟的同一时钟沿采样到数据,保持时间Thd与时钟偏斜之和就必须小于数据稳定时间,这样就满足了保持时间的定义。

这样一不小心解释了同沿分析问题,又解释了为什么满足如下公式:

Tcq + Tcomb > Thd + Tskew

- 1

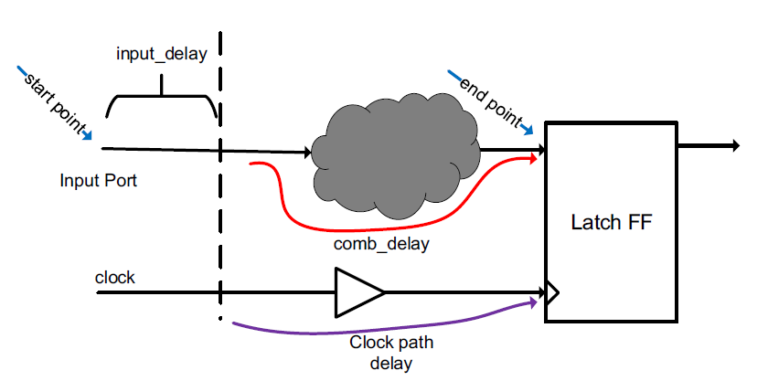

I2R

对于I2R路径,起点将是输入端口,终点将是寄存器的D引脚。 可以假设从输入端口到组合逻辑的输入延迟如下所示。 输入延迟可以包括端口延迟或任何布线延迟。

如果输入端口与外部时钟同步,则可以将路径约束为:

input_delay + comb_delay(max)<时钟延迟路径(时钟偏斜)+ T(时钟的时钟周期)–寄存器FF的建立时间

- 1

并且对于保持约束为

input_delay + comb_delay(min)>寄存器FF的保持时间+时钟延迟路径(时钟偏斜)。

- 1

如果输入与时钟不同步,则该路径可能受到从输入端口到寄存器FF D引脚的路径的最大和最小延迟的约束。 通常,在这种情况下(时钟锁定的同步路径)需要两个背靠背的FF来消除亚稳性问题。

input_delay + comb_delay(max)<max_delay(必须)

input_delay + comb_delay(min)> min_delay(必须)

- 1

- 2

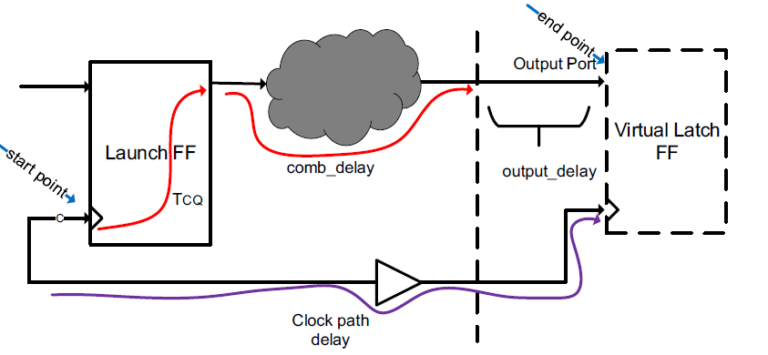

R2O

对于R2O路径,起点将是启动触发器的时钟引脚,终点将是输出端口。 可以从组合逻辑的输出中假设输出延迟,如下所示。 输出延迟可以包括从组合逻辑到引脚的布线延迟。

如果输出端口与时钟同步,则可以设置以下路径:

TCQ + comb_delay(最大值)+ output_delay < 时钟延迟路径(时钟偏斜)+ T(时钟的时钟周期)– 寄存器FF的建立时间

- 1

并且对于保持约束为

TCQ + comb_delay(min)> 寄存器FF的保持时间+时钟延迟路径(时钟偏斜)。

- 1

如果输出路径与时钟不同步,则数据路径可能受到最小和最大延迟的限制。

TCQ + comb_delay(max)+ output_delay <max_delay(必需)

TCQ + comb_delay(min)+ output_delay> min_delay(必需)

- 1

- 2

- 3

I2O

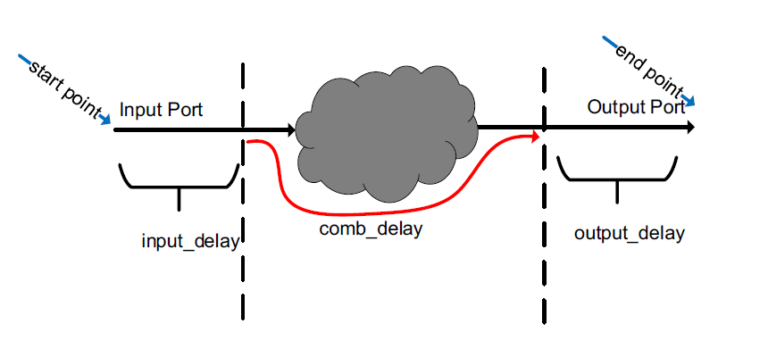

对于I2O路径,起点是输入端口,终点是输出端口。 可以假设输入端口的输入延迟和输出端口的输出延迟。 通常,输入和输出端口之间的组合路径受到约束,以便满足最小和最大延迟约束。

input_delay + comb_delay (max) + output_delay < max_delay (required)

input_delay + comb_delay (min) + output_delay > min_delay (required)

- 1

- 2

- 3

还可以假设虚拟发射触发器驱动输入端口,而虚拟捕获触发器锁存输出端口。 在这种情况下,可以像R2R路径一样进行分析。

静态时序分析技巧和窍门

通过定义时钟开始约束您的设计。

始终为所有主要输入(输入延迟)和主要输出(输出延迟)定义约束。

约束设计中的所有路径。 如果约束文件不完整,则静态时序分析将无法完成。 请记住,静态时序分析适用于垃圾回收原理。

如果从时序角度来看路径不是关键,则可以为这些路径定义时序例外(错误路径,多循环路径等)。

- 通过定义时钟开始约束您的设计。

- 始终为所有主输入(输入延迟)和主输出(输出延迟)定义约束。

- 对设计中的所有路径进行约束。如果约束文件不完整,静态时序分析分析将不完整。请记住,静态时序分析的工作原理是垃圾进垃圾出。

- 如果某条路径从时序角度看并不关键,可以为这些路径定义时序例外(伪路径、多周期路径等)。

邀请路径

同行交流地址:FPGA/IC Technology Exchange

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/113894312

- 点赞

- 收藏

- 关注作者

评论(0)