FPGA的设计艺术(10)HDL是软件还是硬件?

前言

大家都知道HDL是逻辑设计的语言,FPGA开发是一种硬件开发的行为,但由于我们平时也使用某种类似软件的方式管理项目,并且类似软件的行为来编码,大多数人还是会误会?你是不是在搞软件?

对于这种问题,我从来都是尴尬一笑,我是做逻辑的。或者说我是做FPGA开发的?但貌似这种回答并不能说明什么问题?我明明看到你在写代码,你三个大屏幕上都是密密麻麻的代码,这是做硬件或者这是设计电路?

于是,这就有必要说一下,FPGA开发是硬件行为还是软件行为?HDL语言是硬件语言还是软件

注:本文首发地址https://www.ebaina.com/articles/140000010029

HDL:软件还是硬件?

尽管FPGA开发(数字设计)不是软件开发,但过程和管理工具却非常相似。这两项任务实质上是在创建令人难以置信的复杂逻辑结构。

Verilog示例:

always@(posedge sysclk or posedge reset) begin

if(reset) begin

igq_reg <= 1'b0;

end

else begin

igq_reg <= igg_in;

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

同样逻辑的VHDL示例:

p_igq_reg : process( sysclk )

begin

if( rising_edge ( sysclk ) )then

if( reset = '1 ')then igq_reg <= '0 ';

else igq_reg <= igg_in ;

end if;

end process;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

软件的定义是制造完成后可以更改的任何内容。由于可以在完成电路板制造后更改FPGA设计,因此有时将其误称为软件。但是,VHDL和Verilog不是编程语言。HDL的中文名叫硬件描述语言,英文全称为:Hardware Description Language,可见,它的名字就告诉我们,它是为了描述硬件而存在的语言。它们并不是我们在使用软件一词时所想到的东西。

HDL的应用场合有两种,一种是定制芯片,使用HDL设计完成芯片需要实现的功能,芯片制造完成流片后不可更改。另一种应用场合是FPGA设计,使用FPGA这种器件(FPGA本质上也是一种芯片,只不过它是可编程的),在其内部使用HDL语言描述各种逻辑功能的电路,并且可以随时更改设计,相比于芯片更加的灵活。

软件语言可以运行于CPU中,CPU中软件语言的运行,大家都知道,是通过执行指令顺序执行命令。

相对于CPU,下面有必要对FPGA进行简单对比:

我们可以将FPGA看作是大量未连接的数字组件的集合。这包括诸如多路复用器和逻辑门之类的基本组件,以及诸如DSP内核之类的更复杂的组件。在对FPGA进行编程时,实际上是在这些不同组件之间创建连接以创建一个复杂的系统。所有这些意味着我们在创建基于FPGA的设计时从根本上设计硬件。结果,我们可以设计出许多彼此并行运行的电路。这意味着FPGA能够同时执行大量不同的操作。与必须由CPU顺序运行的软件方法相比,这是一个主要优势。

此外,我们还可以在FPGA中对设计时序进行更多控制。我们可以估计在几纳秒内完成一个FPGA需要多长时间。同样,如果我们使用CPU来实现我们的设计,我们将无法做到这一点。这些功能的结果是,FPGA设计比微控制器中的等效实现要快得多。

缺点是它们往往更难以使用。就像我们将要看到的,这不是因为设计FPGA本质上比较困难。主要的区别是开发FPGA的人群要小得多。因此,我们可以使用的库和开放源代码要少得多。

什么是VHDL和Verilog?

VHDL或Verilog同样都是用于描述数字设计的基于文本的语言。 二者同属于HDL,即硬件描述语言,HDL使设计人员无需实际设计硬件即可描述硬件的功能。它们使设计人员可以将行为与实现在各个抽象级别上分开。他们可以准确地描述逻辑门或描述计数器的行为。

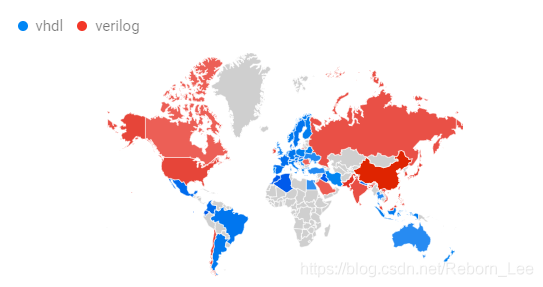

既然都是描述硬件的语言,那么该如何选择呢?关于这个问题,我在博文中也曾经有过介绍:FPGA/ASIC初学者应该学习Verilog还是VHDL?

文章中对此进行数据上的介绍,可以一看。

许多人在学习FPGA设计时遇到的第一个问题是他们应该学习VHDL还是Verilog。对于有志于成为专业FPGA设计人员的任何人,学习这两种语言将是有益的。因此,在这种情况下,一个更重要的问题是首先要学习哪种语言。

虽然这两种语言确实存在许多差异,但是对于初学者来说,这些差异可能太微妙了,无法完全欣赏。实际上,即使对于专业工程师而言,很多时间也将取决于个人喜好或公司内部已有的政策。当涉及到RTL建模时,地理通常是选择学习语言的主要决定因素。Verilog是加利福尼亚大型科技公司最常用的语言。因此,对于希望在那里工作的任何人来说,首先学习Verilog都是有意义的。在欧洲,VHDL被更广泛地使用,从这种语言开始是有意义的。

对于爱好者来说,verilog也是一个不错的选择,因为它通常不太冗长。对于门级建模,Verilog比VHDL更为流行。

这主要是由于它具有定义原语行为的固有能力。这意味着我们可以使用一种称为用户定义原语的语言功能来定义FPGA内单元的行为。这对于必须开发定义其芯片中单元行为的库的芯片供应商尤其有用。

与基于VHDL的同类产品相比,使用基于Verilog的模型进行的仿真也往往具有更快的执行时间。

其实对于HDLs:软件还是硬件这样的问题?这是一个错误的问题。VHDL可以用来描述硬件或编写软件。一个测试台可能包含文件访问例程和文本解析器。这些都是用VHDL编写的软件功能。描述数字设计的HDL只是数字电路设计,是一种硬件技能。关键的一点是,FPGA设计就是数字电路设计。为FPGA编写可靠的、可综合的、高效的、同步的VHDL,需要掌握数字设计技术。不管是HDL形式还是原理图形式,数字设计还是数字设计。

软件和硬件差异

软件是由一个或多个处理器执行的指令列表。源代码被编译为目标代码,但是它仍然是指令列表。数字设计是将逻辑电路放置在集成电路上。 VHDL被合成为逻辑电路,然后被放置在FPGA中并与布线资源连接在一起。 VHDL永远不会执行。电路的相对位置对性能至关重要。

尽管HDL语言通常被称为编程语言,但它们与传统语言几乎没有共同之处。当使用诸如C或Java之类的语言时,我们正在编写一种抽象算法或描述程序行为。CPU实际实现此程序的方式对我们来说不太可能真正有意义。相反,当我们编写HDL代码时,我们是在描述数字电路的行为。在设计FPGA时,请记住这种不同的方法,这一点很重要。

实际上,我们已经用RTL进行一次简单的RTL建模实践。我们从一个基本电路开始,然后写了一些描述电路行为的HDL。

使用RTL方法的设计由描述FPGA内部寄存器之间的数据流的代码组成。

这意味着我们编写了用触发器,逻辑门,有限状态机和RAM明确描述FPGA行为的代码。

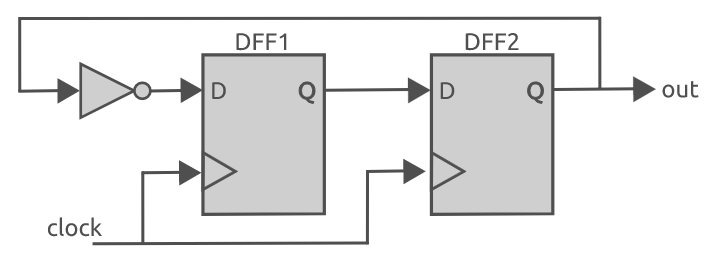

让我们考虑下面的示例电路来演示此概念。

例如,这个电路:

在该电路的RTL模型中,我们将编写描述两个D型触发器和非门的行为的代码。

使用VHDL对其描述为:

dff1_d <= not dff2_q;

dff1:

process (clock) is

begin

if rising_edge(clock) then dff1_q <= dff1_d;

end if;

end process dff1;

dff2:

process (clock) is

begin

if rising_edge(clock) then dff2_q <= dff1_q;

end ill

end process dff2;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

使用Verilog对其描述为:

assign dff1_d = ~dff2_q;

always@(posedge clk) begin:dff1

dff1_q <= dff1_d;

end

always@(posedge clk) begin:dff2

dff2_q <= dff1_q;

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

在此代码中,第一行对非门的行为进行建模。

使用VHDL或Verilog流程对标记为dff1和dff2的触发器进行建模。

只要时钟出现上升沿,这些过程就会锁存输入的值。这符合D型触发器的预期行为。

从该示例中可以看到,我们如何描述设计中组件的行为以及它们之间的互连。

与其他类型的建模(仅定义组件之间的连接)相比,这是RTL建模的定义功能。

软件和硬件的相似性

FPGA中的数字设计每天可以改变很多次,这增加了令人难以置信的灵活性,但代价是有很大的混淆可能性。这意味着对修订控制的强烈需求。关键点:HDL和仿真器使人们很容易用行动代替思想。摒弃这种诱惑,先设计,再编码。

为什么硬件或软件问题很重要?

为了描述数字设计,您无需完全选择。使用综合工具认可的标准语法来编码数字设计非常重要。始终要记住这样一个问题。综合工具将从这些代码中建立什么?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/114768890

- 点赞

- 收藏

- 关注作者

评论(0)