GT Transceiver的复位与初始化(2)CPLL复位以及QPLL复位

CPLL复位

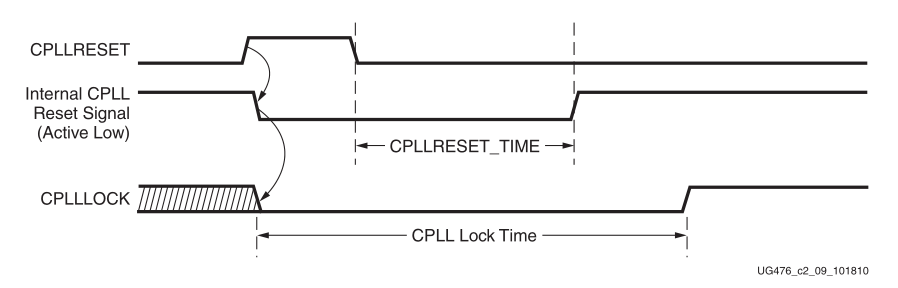

CPLL必须使用CPLLPD端口断电,直到FPGA结构中检测到参考时钟边沿。在CPLLPD无效后,CPLL必须在使用前进行复位。每个GTX/GTH收发器通道有三个专用端口用于CPLL复位。如下图所示,CPLLRESET是一个复位CPLL的输入。CPLLLOCK是一个输出,表示复位过程已经完成。

这个异步CPLLRESET脉冲宽度的指导原则是参考时钟的一个周期。由内部GTX/GTH收发器电路产生的真正的CPLL复位要比CPLLRESET高脉冲持续时间长得多。CPLL锁定所需的时间受一些因素的影响,如带宽设置和时钟频率。

QPLL复位

QPLL复位描述和CPLL几乎一致,就是名词替换:

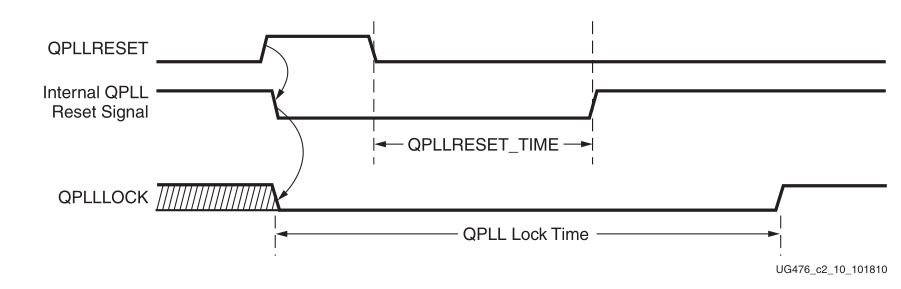

在使用QPLL之前,必须对其进行复位。每个GTX/GTH收发器Quad有三个专用端口用于QPLL复位。

如下图所示,QPLLRESET是一个输入,用于复位QPLL。QPLLLOCK是一个输出,表示复位过程已经完成。

这个异步QPLLRESET 脉冲宽度的指导原则是参考时钟的一个周期。由内部GTX/GTH收发器电路产生的真正的QPLL复位比QPLLRESET高电平脉冲持续时间长得多。QPLL锁定所需的时间受一些因素的影响,如带宽设置和时钟频率。

逻辑短文系列往期博文:

GT Transceiver的复位与初始化(1)Transceiver复位的两种类型和两种模式

GT Transceiver中的重要时钟及其关系(10)RXOUTCLK的来源及其生成

GT Transceiver中的重要时钟及其关系(9)RXUSERCLK和RXUSER_CLK2的生成

GT Transceiver中的重要时钟及其关系(8)TXOUTCLK的来源及其产生

GT Transceiver中的重要时钟及其关系(7)TXUSRCLK以及TXUSRCLK2的产生

GT Transceiver中的重要时钟及其关系(6)TXUSRCLK以及TXUSRCLK2的用途与关系

GT Transceiver中的重要时钟及其关系(5)QPLL的工作原理介绍

GT Transceiver中的重要时钟及其关系(4)CPLL的工作原理介绍

GT Transceiver中的重要时钟及其关系(3)多个外部参考时钟使用模型

GT Transceiver中的重要时钟及其关系(2)单个外部参考时钟使用模型

GT Transceiver中的重要时钟及其关系(1)GT Transceiver参考时钟

FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

高速串行总线设计基础(六)揭秘SERDES高速面纱之数据包与参考时钟要求

高速串行总线设计基础(八)揭秘SERDES高速面纱之CML电平标准与预加重技术

TCL中Ports/Pins/Nets/Cells/Clocks之间的交互关系?

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/120818018

- 点赞

- 收藏

- 关注作者

评论(0)