【计算机组成原理】第六章 总线系统

@toc

总线:构成计算机系统的互联机构,是系统内各功能部件之间进行信息传送的公共通路。

🍫总线的分类

1、按传送的信息分

-

数据总线:双向,三态总线,用于传送数据信息 ;一般与机器字长同位

-

地址总线:单向,三态总线,用于传送地址信息;其位数决定可直接寻址的范围

-

控制总线:传送控制、状态信息

2、按连接部件分

- 内部总线:CPU内部链接各寄存器及运算部件之间的总线

- 系统总线:CPU同计算机系统的其他高速功能部件,如存储器、通道等互相连接的总线

- 通信总线(I/O总线):中、低速I/O设备互相连接的总线

🍫总线标准化

为保证总线的性能充分发挥以及兼容问题而提出的;

主要包括总线的各种特性、数据传输率、总线通信协议、仲裁协议等一系列规定和约定。

典型的标准总线:ISA、EISA、PCI、PCI-express;

按总线标准设计的接口是通用接口。

🍫总线的性能指标

- 总线宽度:一次总线操作中,最多可传送的数据位数。

- 总线周期:一次总线操作所需要的最小间隔时间。总线周期与总线的时钟频率成反比,即T=1/f

- 寻址能力:取决于地址总线的根数。PCI总线的地址总线为32位,寻址能力达4GB

- 负载能力:总线上能够连接的设备数。

是否支持突发传送

总线上数据传送方式:

正常传送——每个传送周期先传送数据的地址,再传送数据。

突发传送——支持成块连续数据的传送,只需给出数据块的首地址,后续数据地址自动生成。

==PCI总线支持突发传送,ISA不支持。==

==总线带宽==

也称为传输率,通常指总线所能达到的最高数据传输率,单位是Bps(每秒传送字节数)

计算公式:Dr=D×f /N

D——数据宽度; f——总线时钟频率;

N——完成一次数据传送所需的时钟周期数。

PCI总线1.0版的总线带宽132MBps

🍫总线仲裁

多个功能模块争用总线时,必须由总线仲裁部件选择一个主设备使用总线。

总线仲裁方式

集中式:由中央仲裁器决定总线使用权的归属。

分布式:多个仲裁器竞争使用总线。

集中式仲裁

- 链式查询方式:设备的优先权与总线控制器的距离有关(在查询链中离总线仲裁器最近的设备具有最高优先级)

优点:硬件连接简单,判优容易,设备增删容易;

缺点:对电路故障敏感,优先级固定(如果高优先级设备频繁请求,那么低优先级设备可能长期不能使用总线); - 计数器定时查询方式:设备的优先权由计数值决定,计数值为0时同链式查询方式;

优点:优先权控制灵活,对电路故障不敏感;

缺点:硬件成本增加,控制复杂度高; - 独立请求方式:设备的优先权由中央仲裁器的内部排队逻辑决定;

优点:响应时间快,即确定优先响应的设备花费的时间少;对优先次序的控制也是相当灵活的;

缺点:硬件复杂度高。

分布式仲裁

分布式仲裁不需要中央仲裁器,由分布在各部件中的多个仲裁器竞争使用总线。

每个潜在的主模块都有自己的仲裁器和唯一的仲裁号,通过仲裁总线上仲裁号的比较,决定可占用总线的部件。

某部件有总线请求时,将其仲裁号发送到共享仲裁总线上;每个仲裁器将仲裁总线上得到的号与自己的号进行比较;如果仲裁总线上的号大,则它的总线请求不予响应,并撤消它的仲裁号;最后,获胜者的仲裁号保留在仲裁总线上。

分布式仲裁是以优先级仲裁策略为基础。

🍫总线传送方式

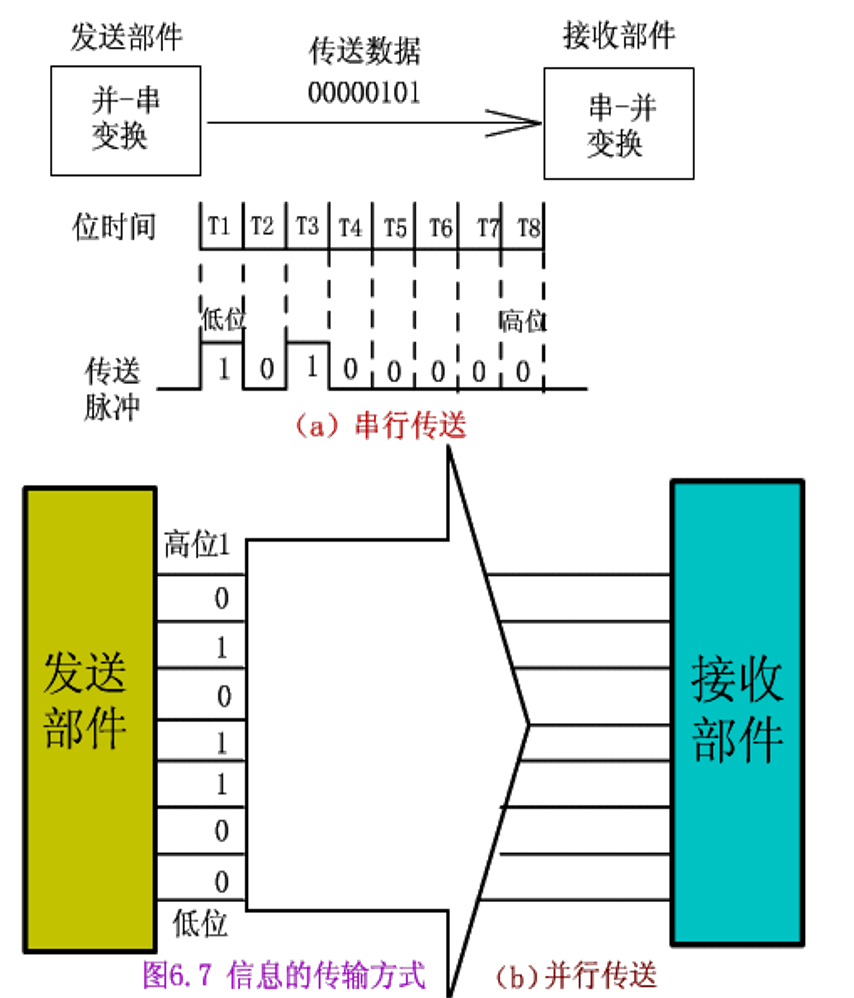

- 串行传送:使用一条传输线,采用脉冲传送。

特点:成本比较低廉,信息传送速度慢; - 并行传送:每一数据位需要一条传输线,一般采用电位传送;

系统总线的信息传送方式。 - 分时传送:

总线传送信息的分时复用:某个传输线上既传送地址信息,又传送数据信息。(例如:CPU中的复用引脚)

共享总线部件对总线的分时复用:在不同的时间内由不同的部件使用总线。(例如:系统中主模块对总线的争用)

🍫接口

接口:I/O设备适配器,指CPU和主存、外围设备之间通过总线进行连接的逻辑部件。

一个适配器必有两个接口,一个同系统总线相连,采用并行方式;另外一个同设备相连,可能采用并行方式或是串行方式。

🍫I/O端口的地址编排方式

存储器统一编址(存储器映像编址):

在这种编址方式中,I/O端口和内存单元统一编址,即把I/O端口当作内存单元对待,从整个内存空间中划出一个子空间给I/O端口,每一个I/O端口分配一个地址码,用访问存储器的指令对I/O端口进行操作。

存储器统一编址的优点是:

I/O端口的数目几乎不受限制;

访问内存指令均适用于I/O端口,对I/O端口的数据处理能力强;

cpu无需产生区别访问内存操作和I/O操作的控制信号,从而可减少引脚。

存储器统一编址缺点是:

程序中I/O操作不清晰,难以区分程序中的I/O操作和存储器操作;

I/O端口占用了一部分内存空间;

I/O端口地址译码电路较复杂(因为内存的地址位数较多)。

I/O独立编址:

I/O端口编址和存储器的编址相互独立,即I/O端口地址空间和存储器地址空间分开设置,互不影响。采用这种编址方式,对I/O端口的操作使用输入/输出指令(I/O指令)。

I/O独立编址的优点是:

不占用内存空间;

使用I/O指令,程序清晰,很容易看出是I/O操作还是存储器操作;

译码电路比较简单(因为I/0端口的地址空间一般较小,所用地址线也就较少)。

I/O独立编址缺点是:只能用专门的I/O指令,访问端口的方法不如访问存储器的方法多。

🍫总线的定时

总线的信息传送过程:请求总线、总线仲裁、寻址、信息传送、状态返回;

定时:确定事件出现在总线上的时序关系;

定时的分类:同步定时、异步定时

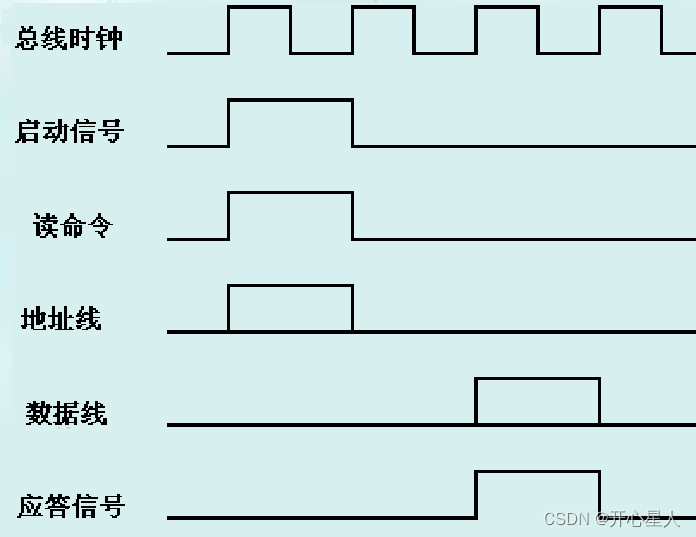

同步定时

系统采用统一的时钟信号,所有事件的出现时间均有该时钟信号确定;

优点:各模块配合简单一致;数据传输效率较高;

缺点:各模块的速度差异较大时,会影响系统的整体工作效率;时钟信号受到干扰时,会引起错误的同步;

适用于总线长度较短,各功能模块速度相差不多的系统。

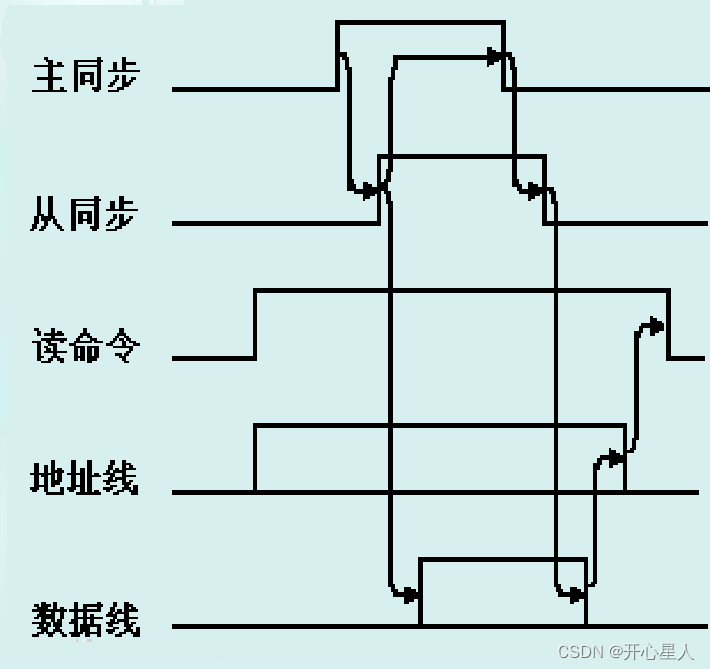

异步定时

系统依靠应答方式或互锁机制来决定事件出现的时间。

优点:总线周期长度可变;

缺点:增加了总线的复杂性和成本;

适用于设备工作速度不一致的系统。

🍫习题练习

1、同步通信之所以比异步通信具有较高的传输速率是因为同步通信( C )

A、不需要应答信号

B、总线长度较短

C、用一个公共时钟信号进行同步

D、各部件存取时间比较接近

2、下列关于多总线结构的叙述中,错误的是(D)

A、靠近CPU的总线速度较快

B、存储器总线可支持突发传送方式

C、总线之间须通过桥接器相连

D、PCI- Express×16采用并行传输方式

3、常见总线标准的英文缩写:ISA、EISA、PCI、PCI-Express

4、下列关于总线设计的叙述中,错误的是(A)

A、并行总线传输比串行总线传输速度快

B、采用信号线复用技术可减少信号线数量

C、采用突发传输方式可提高总线数据传输率

D、采用分离事务通信方式可提高总线利用率

5、下列选项中,可提高同步总线数据传输率的是(B)

I. 增加总线宽度

II. 提高总线工作频率

III. 支持突发传输

IV. 采用地址/数据线复用

A、仅 I、II

B、仅 I、II、III

C、仅 III、IV

D、I、II、III 和 IV

III 突发传输一般表示的是两个设备之间进行数据传送的一种模式,也可将其称为突发模式下的数据传输。而突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。在突发传输模式下,多个数据单元当做一个单元(相当一个数据块)来传送,从而提高了传输效率。

IV 地址数据线复用并非提高而是降低,毕竟同一时间你还得传地址过去,等价的数据传输效率就低了。

6、下列关于I/O接口的叙述,错误的是( D )

A、状态端口和控制端口可以合用同一个寄存器

B、I/O接口中CPU可访问的寄存器称为I/O端口

C、采用独立编址方式时,I/O端口地址和主存地址可能相同

D、采用统一编址方式时,CPU不能用访存指令访问I/O端口

- 点赞

- 收藏

- 关注作者

评论(0)