DMA控制器8237A

1 DMA系统简介

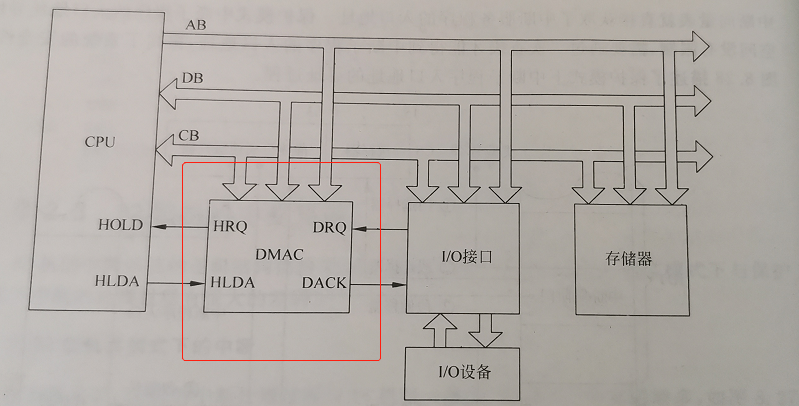

DMA(direct memory access)是一种外设与存储器或者存储器与存储器之间直接传输数据的方式,在进行DMA存取时,CPU让出总线控制权,不在采用输入输出指令的方法进行数据存取,而采用一个专门的硬件DMAC(Direct Memory Access Control)控制电路,减少了中间环节,从而提高了传输速率。

1.1 DMA基本原理

DMA直接实现I/O与存储器之间的数据传送。

①当I/O接口准备好,希望进行DMA操作时,就像DMAC发出DMA请求信号DRQ(DMA Request)

②DMAC将此请求信号转变成对CPU的总线请求信号(Hold Request)

③CPU当前总线执行周期结束,相应DMAC操作,发出应答信号HLDA(Hold Acknowledgment),此时,由DMAC接管对总线的控制

④由DMAC对存储器寻址,并发出相应的控制信号(DACK,/RD,/WR),使存储器与I/O接口之间直接交换数据

⑤在传送一字节数据时,DMAC自动修改存储器地址和传送字节计数器,并检测传送是否结束

⑥DMA传送结束,DMAC向CPU发出结束信号(EOP),并释放总线,使得CPU重新获得总线控制,恢复正常工作

2 DMA控制器8237A

2.1 8237A概述

- 8237A是可编程DMA控制器;

- 每个8237A有4个独立的DMA通道,优先权不同;

- 每个DMA通道有4种工作方式;

- 一次传送的最大长度可达64KB;

- 多个8237A芯片可以级连,用于扩展通道数。

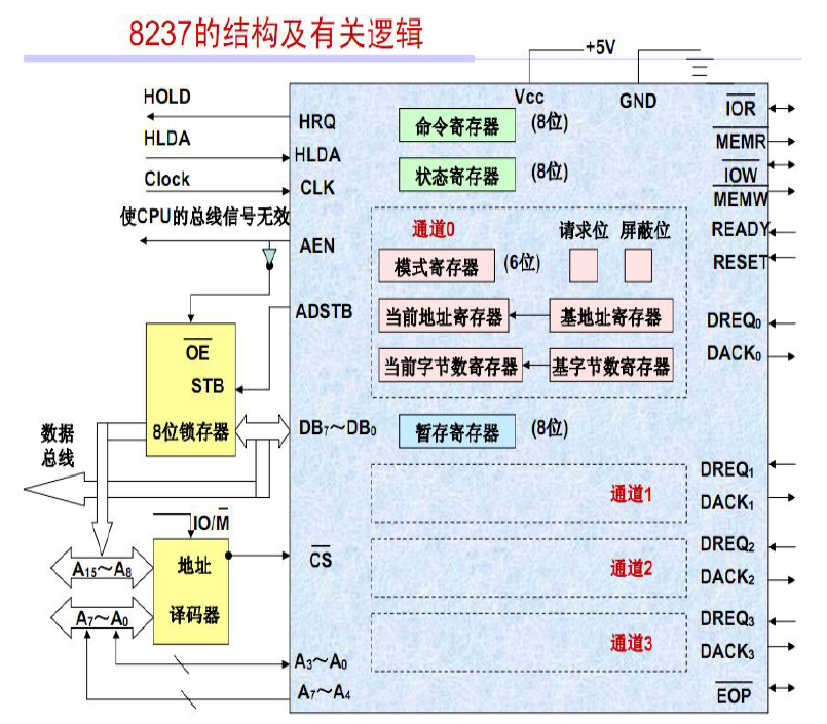

2.2 8237A内部结构

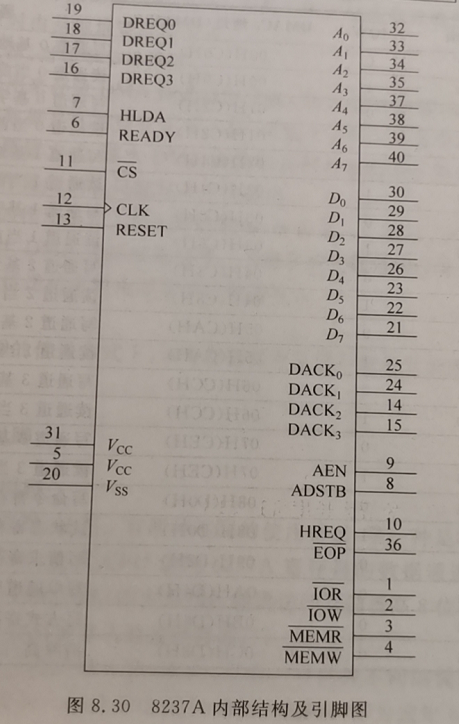

2.3 8237A引脚图

- 控制信号:

(1) CLK:时钟(控制芯片内部操作和数据传输)

(2) ADSTB:地址选通

(3)/cs:片选

(4) READY:准备好

(5) AEN:地址允许

(6)/MEMR:存储器读

(7) RESET:复位

(8)/MEMW:存储器写

(9) /IOR:I/O读

(10)/EOP :过程结束

(11) / IOW :I/O写 - 请求和响应信号

(1) DREQ~0~~DREQ~3~:DMA通道请求

(2) HRQ:总线请求

(3) HLDA:总线响应

(4) DACK~0~~DACK~3~:DMA通道响应 - 数据和地址信号

(1) A~0~~A~7~:地址线

(2) DB~0~~DB~7~:数据线

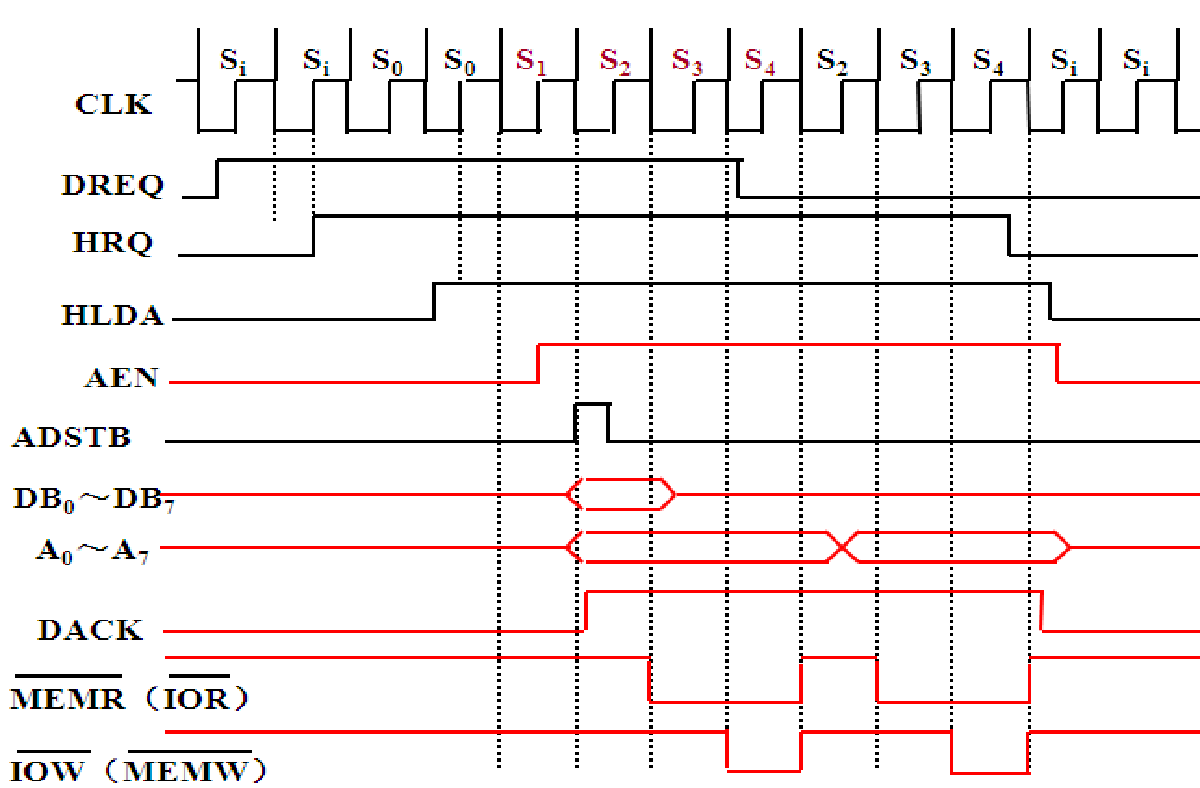

2.4 8237A传送时序

(1) Si状态:空闲周期,Si的下降沿检测到有一个或几个DREQ请求,在Si的下一个上升沿向CPU发出DMA请求,HRQ有效;

(2) S0状态:等待CPU对总线请求的响应,S0的上升沿采样到HLDA信号有效, 下一周期进入S1状态;

(3) S1状态:地址允许信号AEN有效,存储单元高8位地址通过DB0~DB7输出,发出地址选通信号ADSTB,下降沿对高8位地址进行锁存,地址低8位/由地址线A0~A7 输出,且整个DMA传送期间保持;

(4) S2状态:8237A向外设输出DMA响应信号DACK,读写信号相继有效;

(5) S3状态和S4状态进行数据传送;

(6) 块传送方式下:S4后传送下一个字节 ,地址高8位不变,低8位变化,不需要S1直接进入S2,直到发生TC事件。

(7) 若S4之前不能完成数据传送,可令READY为低,在S3和S4之间插入Sw,以加宽DMA传送周期。

2.5 8237A工作方式

2.5.1 单字节传送方式

(1) 传送过程:8237A获取总线控制权后,传送一个字节,字节数寄存器减1,地址寄存器加1或减1,HRQ变为无效,释放总线,HRQ很快再次有效,接收到HLDA有效信号后,传送下一字节,重复以上过程,直到字节数从0减到FFFFH,发生TC事件,DMA传送结束。

(2) 特点:效率低,但能保证两次DMA传送之间CPU有机会重新获取总线控制权。

2.5.2 块传送方式

(1) 传送过程:由DREQ启动后就连续传送数据,直到TC事件发生或外部输入有效的/EOP信号为止。

(2) 特点:一次请求能传送一个数据块,效率高;但整个DMA传送期间CPU长时间无法控制总线。

2.5.3请求传送方式

连续传送数据,当出现以下三种情况之一时停止。

(1) 字节数寄存器从0减到FFFFH,发生TC事件;

(2) 由外部送来一个有效的 信号;

(3)外部输入的DREQ信号变为无效。

当第三种情况发生时,当外设准备好数据后,传送可以继续下去。

特点:DMA操作可由外设控制传送的过程。

2.5.4 级联传送方式

若干片8237A构成主从式DMA系统

2.6 8237A传送类型

- DMA读:数据由存储器传送到外设

- DMA写:外设输入的数据写入存储器

- DMA检验:空操作,时序信号、地址信号与读写时一样,但读写控制线无效,常用于校验。

- 存储器到存储器传送:通道0为源,通道1为目的,软件启动,每传送一个字节需8个时钟周期,前4个时钟周期用于从源区将数据读入8237A的临时寄存器,后4个时钟周期把临时寄存器中的数据写入目的区,直至TC事件发生或发来/EOP信号。

2.7 8237A寄存器组

- 现行地址寄存器:用于保存DMA传送的当前地址值。

- 现行字节数寄存器:保存着还要传送的字节数。

- 基地址寄存器:保存现行地址初值。

- 基字节数寄存器:保存现行字节数初值。

- 模式寄存器:保存相应通道模式控制字。

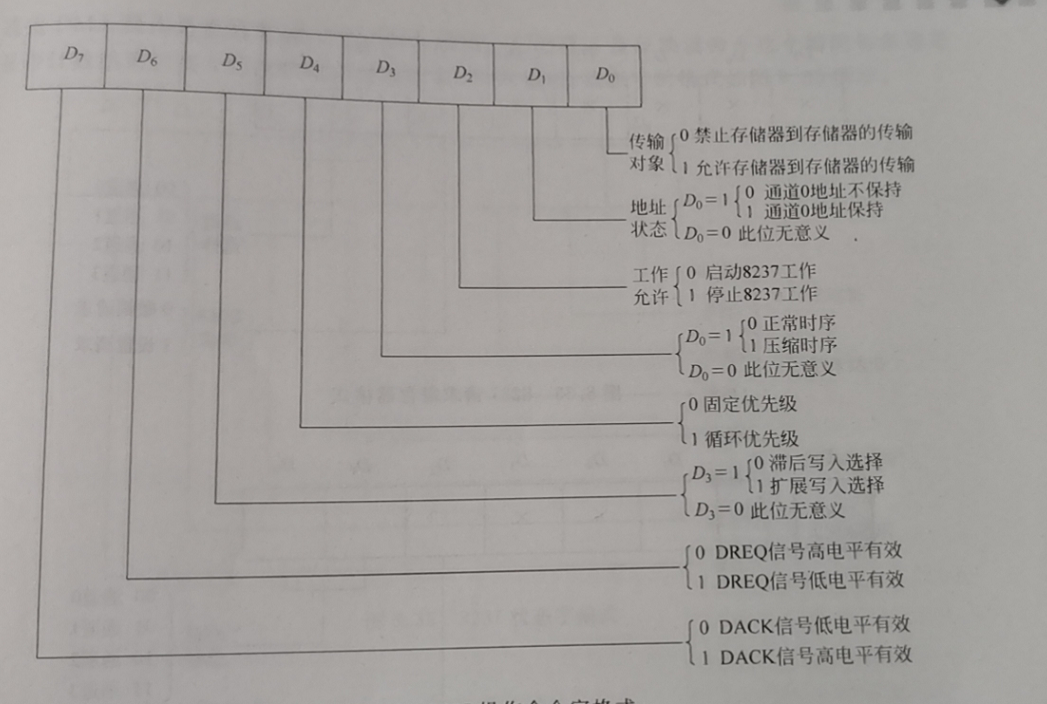

- 命令寄存器:设置8237A操作方式

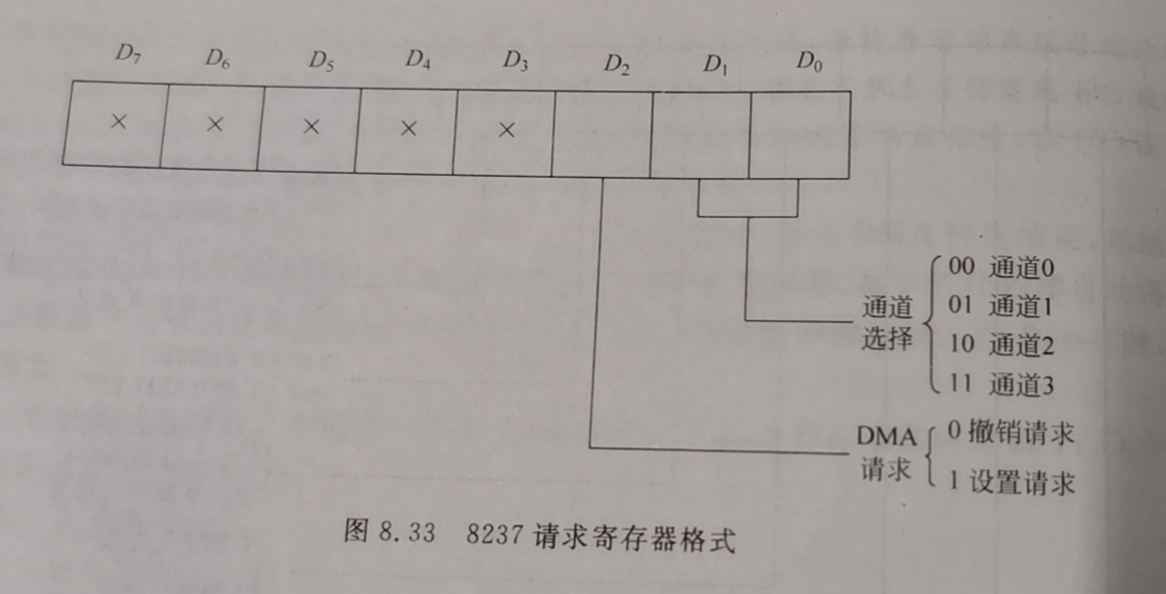

- 请求寄存器:数据块传送时可由软件发出DREQ请求,存储器到存储器传送时,必须由软件请求启动通道0。

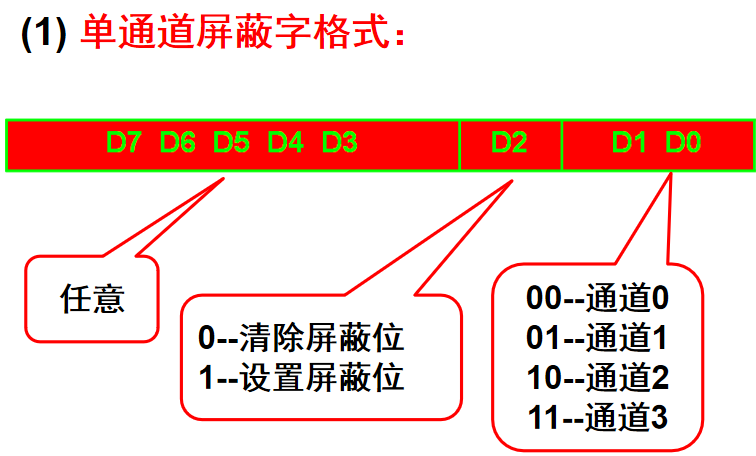

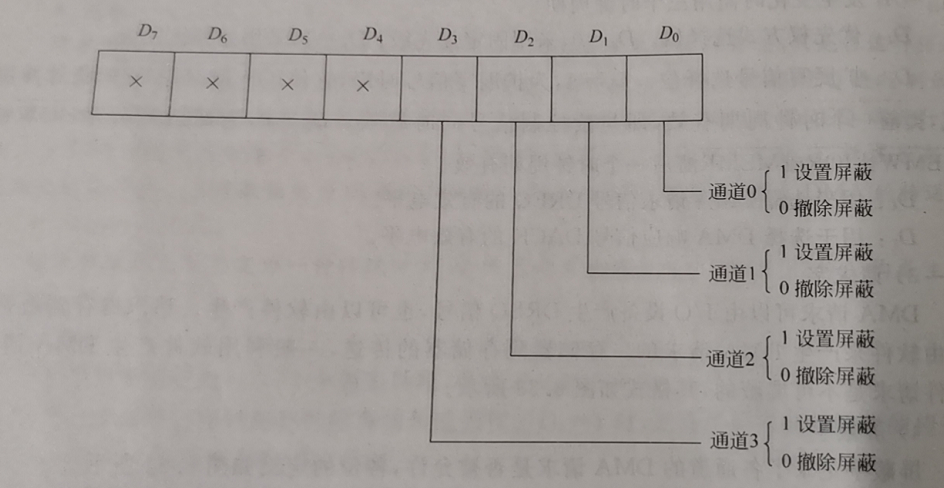

- 屏蔽寄存器:用于屏蔽外设发出的DREQ请求。

(2) 主屏蔽字格式

- 状态寄存器:从CPU读取8237A的工作状态 。

- 临时寄存器: 在存储器到存储器传送方式下,保存数据

2.8 8237A的软件命令

237A共有10种内部寄存器,对它们的操作有时需要配合3个软件命令。8237A “软件命令”的特征:

(1) 不需要通过数据总线写入控制字;

(2) 直接由地址和控制信号译码实现。

- 清除高/低触发器软件命令

高/低触发器控制16位寄存器的读写:

触发器为0,操作低字节;

触发器为1,操作高字节;

16位寄存器进行一次操作,触发器

状态自动改变;

A3A2A1A0=1100,高/低触发器清零。 - 主清除命令

与硬件的RESET信号具有相同的功能,

A3A2A1A0=1101 - 清屏蔽寄存器命令

使4个屏蔽位都清零(允许DMA请求)

A3A2A1A0=1110

- 点赞

- 收藏

- 关注作者

评论(0)