Verilog HDL语法汇总(FPGA-EDA)

本文知识点运行环境以Quartus Prime为例

module内基础设置

module——endmodule是基于模块构成的语法

module模块名(端口1,端口2,端口3,……);

注意module后面有分号

input输入端口,output输出端口,inout输入输出端口

Verilog中关键字都是小写

常量数字编写

二进制: 10'b1010

十进制: 10'd23

十六进制: 10'hB5F

较长数字可以用下划线分开,如: 8'b1010_0010;

数据类型

0:低电平,逻辑0,逻辑非

1:高电平,逻辑1,逻辑真

x:不确定或未知逻辑

z:高阻态

wire型变量、reg型变量,integer型变量

input适用 wire

output适用: wire、reg、integer

内部信号适用: wire、reg

assign对应wire,门元件模块输出端一定是wire

always或者initial中赋值语句一定是reg或者integer

paramater定义符号常量,个人感觉类似于C语言中的const

注意:数组不能作为module的输入输出

运算符

逻辑与:&&; 逻辑或:||; 逻辑非:!;

按位取反:~; 按位与:&; 按位或:|; 按位异或:^; 按位同或:^~;

<小于 <=小于或等于 >大于 >=大于或等于

==等于 !=不等于 ===全等 !==不全等

注意:“<=”也表示信号的一种赋值操作;

>>右移 <<左移

三目运算符:

signal=condition?true_expression:false_expression;

条件成立取1,不成立取2

{}位拼接符

过程语句

initial:仅执行一次

always:会不断的执行

always@(in0 or in1),括号内位敏感信号表达式,内部一发生变化always便执行一次

posedge:上升沿 negedge:下降沿

assign为持续赋值语句,assign c=a&b;这一句话中,a和b任意发生改变,c就发生改变

非阻塞赋值:b<=a

阻塞赋值:b=a;

块语句符号:begin-end

顺序块是自上往下的,采用阻塞赋值

并行块是几乎同时完成的

if-else语句:条件语句必须在always或initial过程块中使用

case语句:default可有可无

严格程度:case>casez>casex

循环语句

forever:连续地执行语句,多用在initial中

repeat:连续执行一条语句n次

while:类似于C语言内使用

for:有条件的循环语句(支持绝大多数综合器)

任务与函数

task:任务的定义与调用都在一个module模块中,调用次数不限,在调用时需要单独配置其输入输出端口

function:返回一个值

仿真与验证

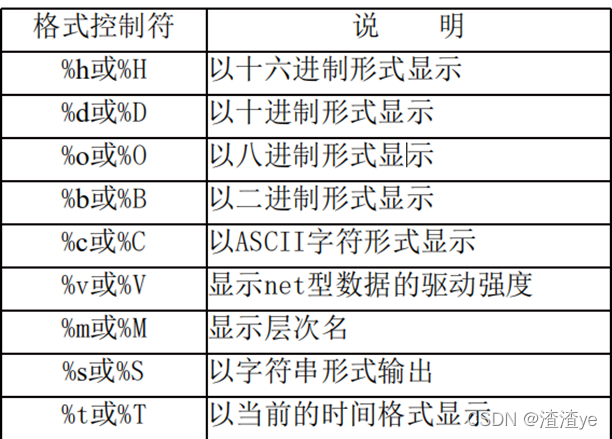

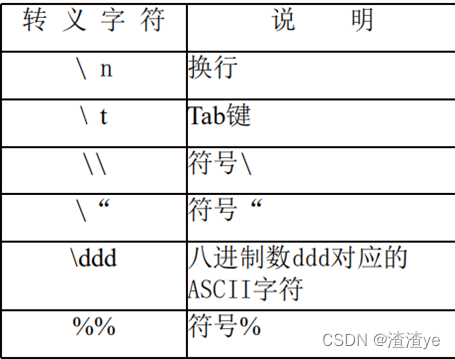

$display,$monitor,显示当前变量值

$display("%b+%b=%b",a,b,sum);

$monitor("data_display=%hhex%ddecimal",100,100);

仿真时间:$time(返回整数),$realtiome(返回实数)

monitor监测任务用于持续监测指定变量

结束或暂停:$finish,$stop

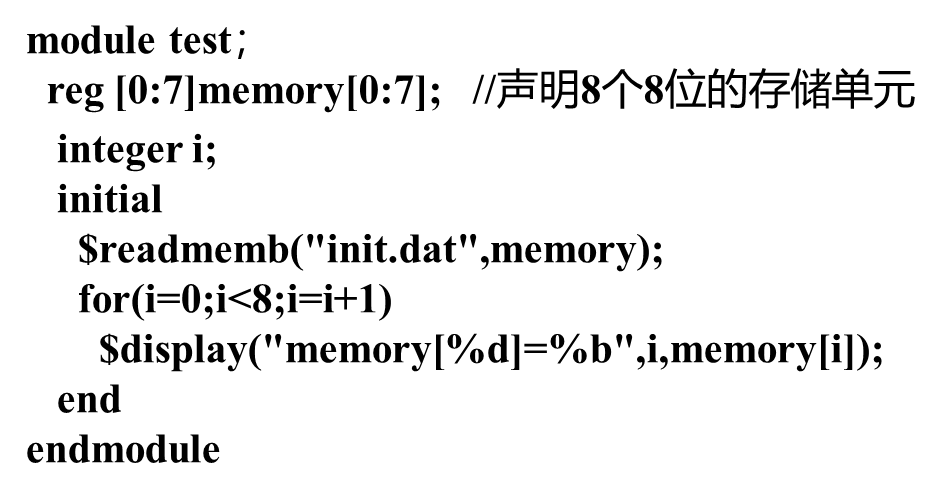

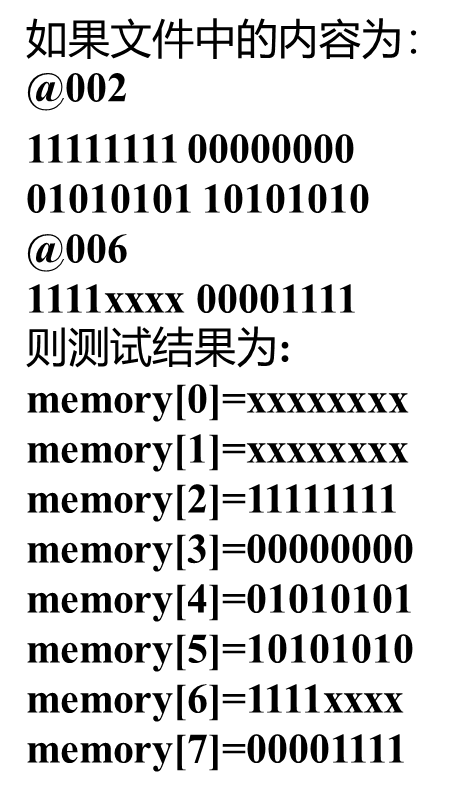

读取数据:$readmemb,$readmemh;

例如:

随机函数:$random

时间标尺定义`timescale<时间单位>/<时间精度>

`timescale 1ns/1ns

含义为:时间延迟单位为1ns,时间精度为1ns(即精确到1ns,整数值)

`timescale编译置零在模块外部出现,并且影响后面所有的时延值。

`timescale 1ns/100ps

含义为:时间延迟单位为1ns,时间精度为100ps(即精确到0.1ns,小数点后1位小数)

文章来源: blog.csdn.net,作者:渣渣ye,版权归原作者所有,如需转载,请联系作者。

原文链接:blog.csdn.net/yyfloveqcw/article/details/124158040

- 点赞

- 收藏

- 关注作者

评论(0)