CC2530的硬件功能及实例讲解

(1)CC2530介绍和功能模块

CC2530 是用于2.4-GHz IEEE 802.15.4、ZigBee 和RF4CE 应用的一个真正的片上系统(SoC)解决方案。

| CPU和内存相关模块 |

CC253x芯片系列中使用的8051 CPU内核是一个单周期的8051兼容内核。它有三种不同的内存访问总线(SFR,DATA 和CODE/XDATA),单周期访问SFR,DATA 和主SRAM。它还包括一个调试接口和一个18 输入扩展中断单元。 |

| 外设、时钟和电源管理模块 |

数字内核和外设由一个1.8-V 低差稳压器供电。它提供了电源管理功能,可以实现使用不同供电模式的长电池寿命的低功耗运行。有五种不同的复位源。 |

| 无线设备 |

具有一个IEEE 802.15.4 兼容无线收发器。RF 内核控制模拟无线模块。另外,它提供了MCU 和无线设备之间的一个接口,这使得可以发出命令,读取状态,自动操作和确定无线设备事件的顺序。 |

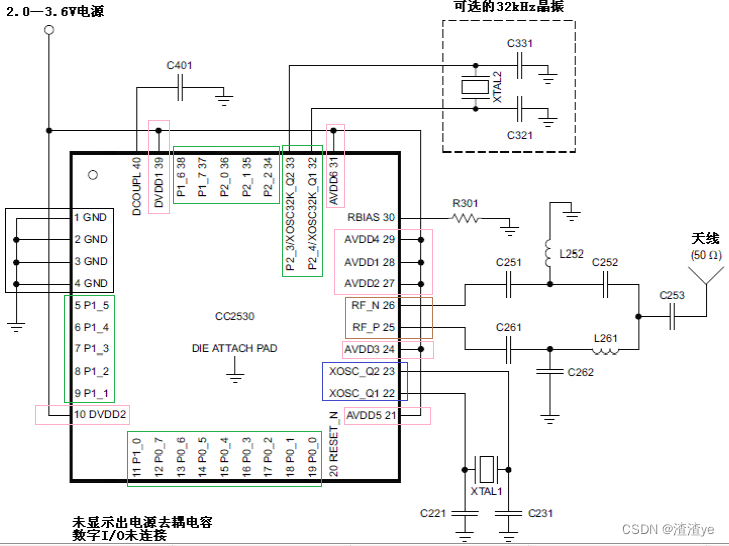

(2)CC2530的具体连接示意

硬件连接示意图

GND - 接地 接地衬垫必须连接到一个坚固的接地面。

GND 1,2,3,4 未使用的引脚 连接到GND

AVDD1 28 电源(模拟) 2-V–3.6-V 模拟电源连接

AVDD2 27 电源(模拟) 2-V–3.6-V 模拟电源连接

AVDD3 24 电源(模拟) 2-V–3.6-V 模拟电源连接

AVDD4 29 电源(模拟) 2-V–3.6-V 模拟电源连接

AVDD5 21 电源(模拟) 2-V–3.6-V 模拟电源连接

AVDD6 31 电源(模拟) 2-V–3.6-V 模拟电源连接

DVDD1 39 电源(数字) 2-V–5-V 数字电源连接

DVDD2 10 电源(数字) 2-V–5-V 数字电源连接

DCOUPL 40 电源(数字) 1.8V 数字电源去耦。不使用外部电路供应。

P0_0 19 数字I/O 端口0.0

P0_1 18 数字I/O 端口0.1

P0_2 17 数字I/O 端口0.2

P0_3 16 数字I/O 端口0.3

P0_4 15 数字I/O 端口0.4

P0_5 14 数字I/O 端口0.5

P0_6 13 数字I/O 端口0.6

P0_7 12 数字I/O 端口0.7

P1_0 11 数字I/O 端口1.0-20-mA 驱动能力

P1_1 9 数字I/O 端口1.1-20-mA 驱动能力

P1_2 8 数字I/O 端口1.2

P1_3 7 数字I/O 端口1.3

P1_4 6 数字I/O 端口1.4

P1_5 5 数字I/O 端口1.5

P1_6 38 数字I/O 端口1.6

P1_7 37 数字I/O 端口1.7

P2_0 36 数字I/O 端口2.0

P2_1 35 数字I/O 端口2.1

P2_2 34 数字I/O 端口2.2

P2_3 33 数字I/O 模拟端口2.3/32.768 kHz XOSC

P2_4 32 数字I/O 模拟端口2.4/32.768 kHz XOSC

RBIAS 30 模拟I/O 参考电流的外部精密偏置电阻

RESET_N 20 数字输入 复位,活动到低电平

RF_N 26 RF I/O RX 期间负RF 输入信号到LNA

RF_P 25 RF I/O RX 期间正RF 输入信号到LNA

XOSC_Q1 22 模拟I/O 32-MHz 晶振引脚1外部时钟输入

XOSC_Q2 23 模拟I/O 32-MHz 晶振引脚

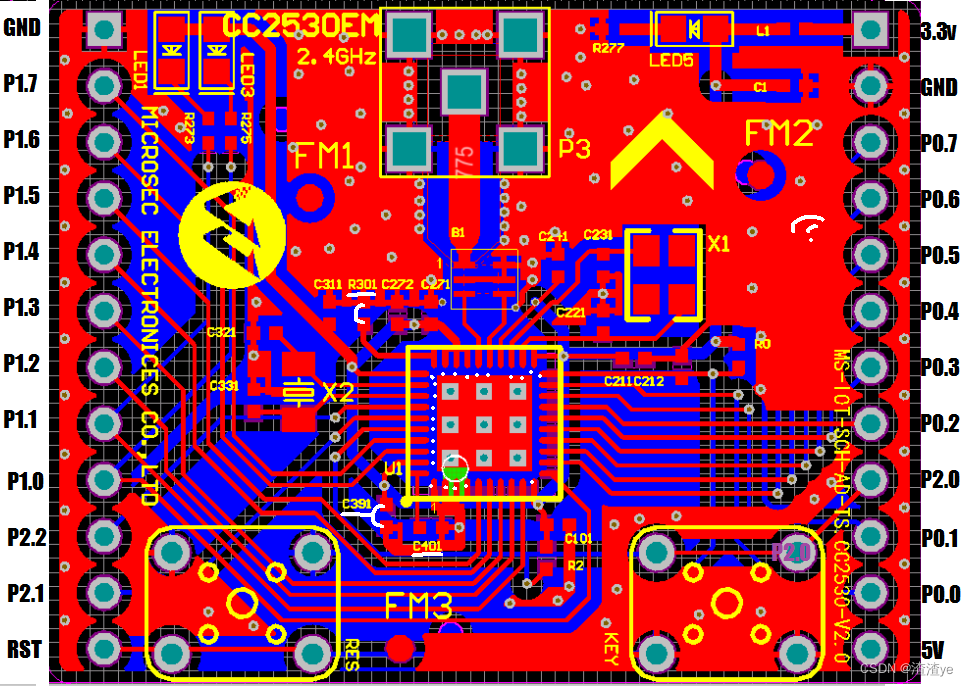

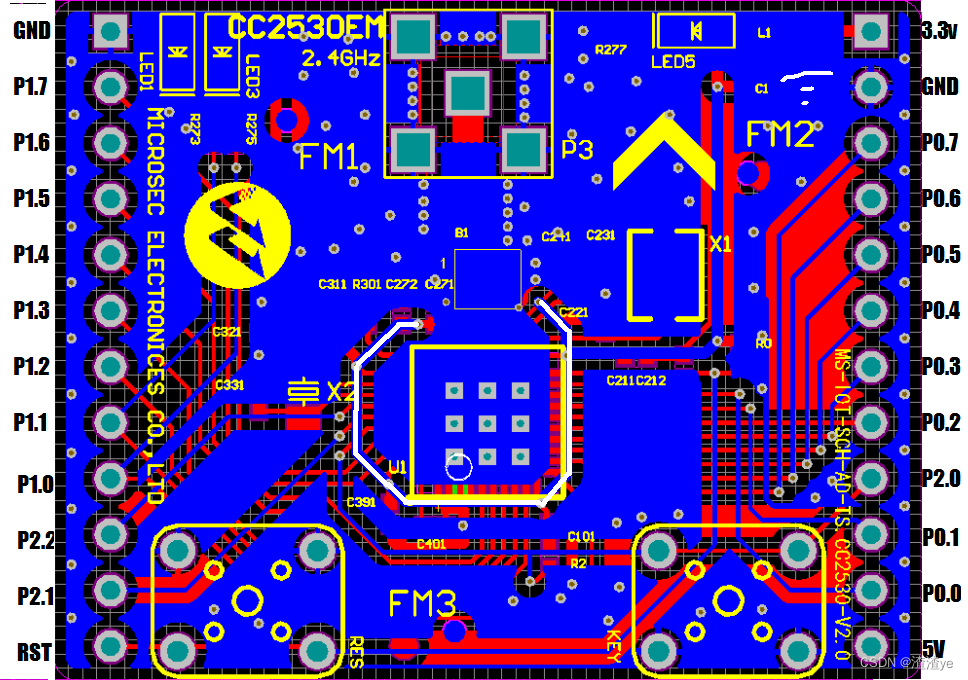

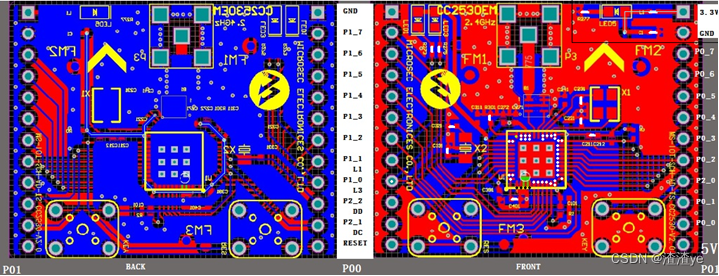

(3)研究CC2530核心板

CC2530一共有40个引脚。其中19个作为数据引脚,接地4个,电源8个,晶振2x2=4个,去耦2个,天线2个,重启1个。

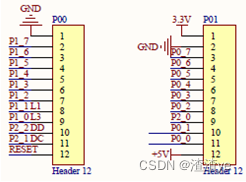

不过核心板只有24个引脚引出。P00端包括RESETx1,GNDx1,P1_0~P1_7(8条引出,其中P1_0和P1_1是核心板上两盏灯),P2_1和P2_2;P01端包括3.3V,5V(5V没用,主要是用来给传感器使用的),GNDx1,P0_0~P0_7(8条引出)以及P2_0(核心板中断开关没有引出)。

没有引出的线:P2_2和P2_3用来连接可选晶振,RF_N和RF_P连接天线,RBIAS和DCOUPL不引出,XOSC_Q1和XOSC_Q2连接晶振。

所以40-(晶振)4-(去耦)2-(天线)2-(GND)(4-2)-(3.3V)(8-1)+(5V)1=24。

上图可以看出如下几个问题:

- CC2530芯片管脚4、10、39等数字电源管脚与21、24、27、28、29、31等电源管脚应就近接滤波电容。

- 片内1.8V稳压器为所需电路提供1.8V电压,1.8V稳压器需用一个去耦电容,以提高电源工作的稳定性,在电路设计中通过CC2530芯片管脚40接一个1μF的电容实现。

- 用1个32MHz的石英谐振器和2个电容(管脚22和23)构成一个32MHz的晶振电路。

- 用1个32.768kHz的石英晶振器和2个电容(管脚33和32)构成一个32.768kHz的晶振电路。

- 关于电感L1:P01_1(3.3V)接入之后首先接了一个电感L1。这里的作用是滤波。【原理】电感是靠储存在电感内的能量滤波。当外来高电压加在电感时,电感会产生反向自感电势抵消外来电压;当外来低电压断开电感时,电感会产生正向自感电势增加外来电压;因此有恒电流的特性,通过它的电流不能突变。在电路中起平波的作用。高频信号难以通过电感。

- 关于电容:在3.3V和GND之间有好几个电容,作用是去耦。去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。

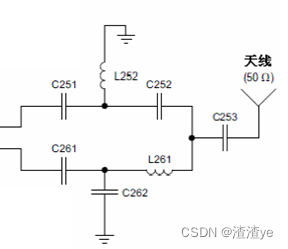

- 巴伦电路:巴伦是平衡不平衡转换器(balun)的英文音译,balun是由“balanced”和“unbalanced”两个词组成的。其中balance代表差分结构,而un-balance代表是单端结构。巴伦电路可以在差分信号与单端信号之间互相转换。CC2530芯片RF_P与RF_N管脚是一对差分输入输出信号,若所使用的天线是不平衡单极子天线,须使用巴伦匹配电路来进行射频收发信号的匹配,可以采用分立电容或者电感,不过这里直接使用巴伦元件来替代。

- 5V引脚在核心板无用,这是为了兼容传感器的扩展板。

文章来源: blog.csdn.net,作者:渣渣ye,版权归原作者所有,如需转载,请联系作者。

原文链接:blog.csdn.net/yyfloveqcw/article/details/124489376

- 点赞

- 收藏

- 关注作者

评论(0)