【嵌入式Linux学习】8、多文件编译与Makefile初探

一、编译链接

正式开始之前呢,先回顾一下程序编译和链接的过程。

源文件【.c】首先会生成中间目标文件【.o】,再由中间目标文件生成执行文件。

在编译时,编译器只检测程序语法以及函数、变量是否被声明。如果函数未被声明,编译器会给出一个警告,但可以生成Object File。而在链接程序时,链接器会在所有的Object File中找寻函数的实现,如果找不到,那到就会报链接错误码(Linker Error)。

二、makefile介绍

Makefile 文件用来告诉计算机,当输入make命令时,需要怎样去编译和链接程序。

1、规则:

- 如果这个工程没有编译过,那么我们的所有C文件都要编译并被链接。

- 如果这个工程的某几个C文件被修改,那么我们只编译被修改的C文件,并链接目标程序。

- 如果这个工程的头文件被改变了,那么我们需要编译引用了这几个头文件的C文件,并链接目标程序。

当Makefile写得够好,所有的这一切,我们只用一个make命令就可以完成,make命令会自动智能地根据当前的文件修改的情况来确定哪些文件需要重编译,从而自己编译所需要的文件和链接目标程序。

2、makefile的语法格式:

target... : prerequisites ...

command

...

- 1

- 2

- 3

target也就是一个目标文件,可以是Object File,也可以是执行文件。还可以是一个标签(Label)。

prerequisites就是,要生成那个target所需要的文件或是目标。

command也就是make需要执行的命令。(任意的Shell命令)

makefile最本质的一个就是所谓的“依赖”关系,target这一个或多个的目标文件依赖于prerequisites中的文件,其生成规则定义在command中。说白一点就是说,prerequisites中如果有一个以上的文件比target文件要新的话,command所定义的命令就会被执行。

三、makefile牛刀小试

Makefile

main:main.o add.o

gcc main.o add.o -o main

rm -rf *.o

- 1

- 2

- 3

main.c

#include "stdio.h"

#include "add.h"

int main()

{

int a = 5, b =8;

printf("result:%d\n",add(a,b));

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

add.c

int add(int a,int b)

{

return a+b;

}

- 1

- 2

- 3

- 4

- 5

add.h

#ifndef __ADD_H__

#define __ADD_H__

int add(int a,int b);

#endif

- 1

- 2

- 3

- 4

- 5

- 6

- 7

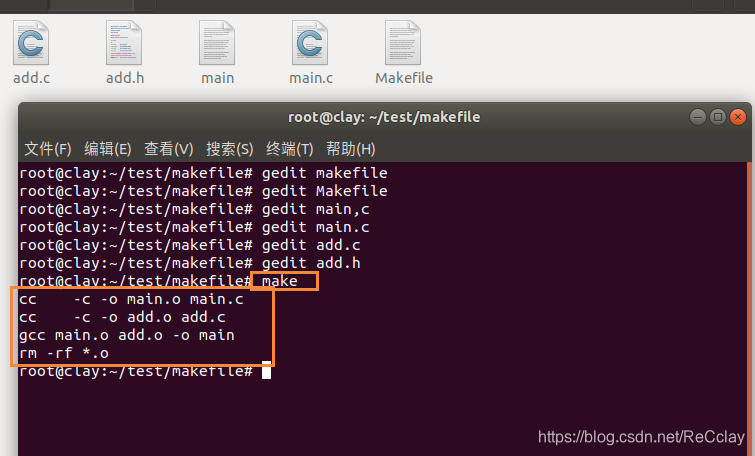

创建以上文件完毕后,在命令行输入make命令进行编译链接…

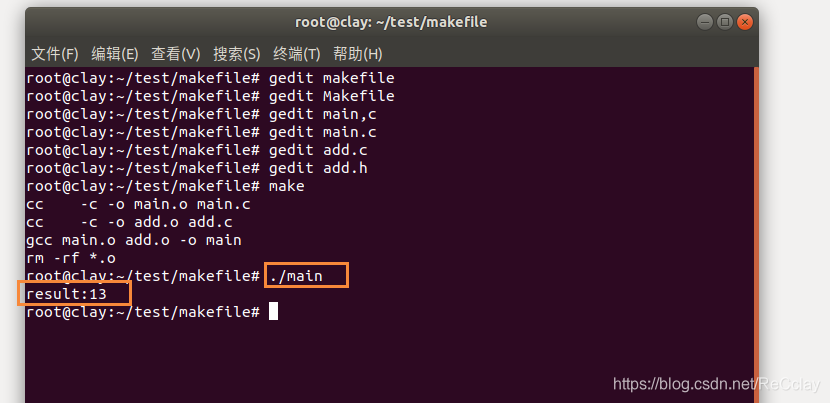

而后输入命令./main,执行可执行文件

文章来源: recclay.blog.csdn.net,作者:ReCclay,版权归原作者所有,如需转载,请联系作者。

原文链接:recclay.blog.csdn.net/article/details/101700762

- 点赞

- 收藏

- 关注作者

评论(0)