【ASIC设计】FPGA小知识拾遗(不断更新...)

【摘要】

ASIC - 专用集成电路

FPGA开发流程

1、设计定义

要做什么?实现什么功能? 2、设计输入

Verilog/VHDL硬件描述语言、成熟的IP核、画原理图的方式进行逻辑设计 3...

ASIC - 专用集成电路

FPGA开发流程

- 1、设计定义

- 要做什么?实现什么功能?

- 2、设计输入

- Verilog/VHDL硬件描述语言、成熟的IP核、画原理图的方式进行逻辑设计

- 3、分析和综合

- 语法检查、逻辑检查

- 生成网表文件

- 4、功能仿真(行为级仿真)(前仿真)

- 能否实现功能?

- 理想仿真,逻辑之间零延迟

- modelsim-altera

- 5、布局布线

- 设计代码对应到FPGA,并完成连线

- 6、时序仿真(门级仿真)

- 考虑延迟,验证布局布线之后电路是否满足时序要求

- modelsim-altera

- 不满足时序要求解决办法:

- ①、调整设计输入,减少组合逻辑电路,如插入寄存器以形成流水线的方式

- ②、进行时序约束,如某段路必须多久走完,这样布局布线就会满足时序要求

- 7、IO分配以及配置文件生成

- 8、配置FPGA(烧写FPGA)

- 9、在线调试

- 嵌入式逻辑分析仪

- 信号探针

- 内存查看

常见FPGA厂商及旗下软件

Xilinx

- ISE、 vivado

Altera【Intel FPGA】

- Quartus II、 Quartus Prime

Lattice

- Diamond、 Mico System

典型的 FPGA 通常包含三类基本资源

- 1、可编程逻辑功能块:是实现用户功能的基本单元,多个逻辑功能块通常规则地排成一个阵列结构,分布于整个芯片;

- 2、可编程输入/输出(I/O)块:完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列四周;

- 3、可编程内部互连资源:包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。用户可以通过编程决定每个单元的功能以及它们的互连关系,从而实现所需的逻辑功能。

不同厂家的逻辑单元叫法

- ALTER的逻辑单元一般叫 LE

- XILINX的逻辑单元一般叫 CLB

Altera【Intel FPGA】常见系列器件

- Stratix (V,IV)

- Arria (10,V GZ,V,II GZ,II GX)

- Cyclone (10 LP,V,IV E,IV GX)

- MAX (10,V,II)

Altera【Intel FPGA】在用系列器件型号记录

- Cyclone IV E FPGA 芯片 EP4CE10F17C8

- Cclone V FPGA 芯片 5CSEBA2U19I7

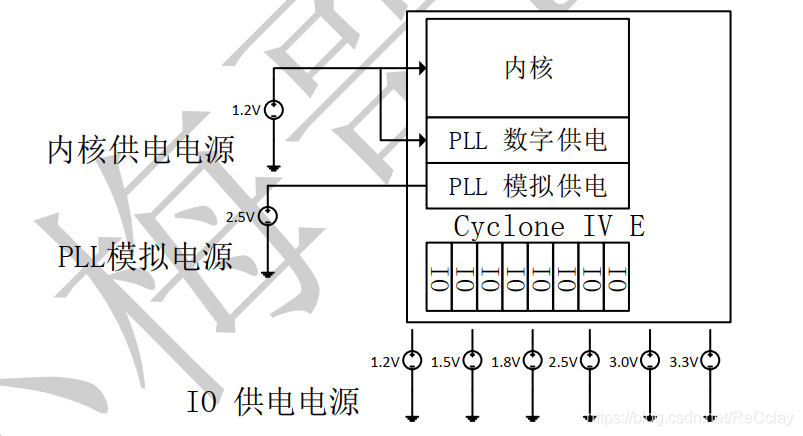

Cyclone IV E FPGA【Intel FPGA】 一般需要三组供电

- ①、内核供电

- 内核供电电压根据器件是否为低电压版本区分, 低电压版本,内核供电为 1.0V,非低电压版本供电为 1.2V

- ②、PLL 模拟电路供电

- PLL 模拟部分供电为固定的 2.5V

- ③、IO 单元供电

- IO 供电电压值从 1.2V~3.3V, 共有 6 种可选值

Altera【Intel FPGA】的Quartus发展变化追溯

- 随着器件系列多样化,从 Quartus II 10.0 以后的版本器件支持包需要单独下载并可根据需要选择性安装

- 在时序仿真软件方面,在 9.1 之前均自带仿真组件,在之后均需下载额外的诸如 Modelsim 或者 Modelsim-Altera 等仿真软件

- Quartus II 12.0 及之前的软件需要额外下载 Nios II 组件,之后的 Quartus II 软件开始自带 Nios II 组件。

- Quartus II 9.1 之前的版本均自带 SOPC 组件,而 Quartus 10.0 自带了 SOPC 和 Qsys 两个组件,但从 10.1 开始,Quartus II 只包含 Qsys 组件。

- 自从 15.1 开始 Quartus II 正式更名为 Quartus Prime。 该版本是 Altera 被 Intel 收购后发布的第一个版本也被官方称为有史以来最大的更新,相比之前加入了 Intel 为 FPGA 专门设计的OpenCL SDK、 SoC Embedded Design Suite 以及 DSP Builder 等组件。

- 到了 16.1 版本,软件连安装目录也从自动命名的 altera 变为 intelFPGA,令人唏嘘不已,感叹发展之快

Quartus 常见源文件

- HDL 文件(Verilog HDL File)

- 原理图文件(BDF 文件)

- TCL文件

- ROM 初始化(mif)文件

- Signaltap II 文件

Quartus 常见生成文件

- .sof 格式文件

- .jic 格式文件

- sof 文件转化为 jic文件,以固化到 EPCS 存储器中

- .bdf文件

- 原理图文件

- .v/.vhd

- 硬件描述语言文件

- .qar 格式文件

- Archive Project选项,将当前工程的所有文件打包为一个 qar 格式的文件,方便保存和传输。

常见仿真

- 寄存器传输级仿真(RTLSimulation)

- 寄存器传输级仿真也被称为功能仿真或前仿真,主要针对没有经过布局布线的 RTL 描述代码。 该仿真结果为理想仿真结果,不含任何布局布线的延迟信息。 一般代码编写完成后都要先进行寄存器传输级仿真,以确定设计的功能逻辑没有问题。

- 门级仿真 Gate Level Simulation。

- 门级仿真是针对 Quartus 编译完成后含布局布线延迟的文件进行仿真,其仿真结果已经与实际在对应器件上的运行结果非常的接近了,具有较大实际参考意义。

网表视图

- RTL 视图

- 查看 RTL 视图, 可以对设计所实现的逻辑功能以类似电路原理图的形式进行核对确认。

- 网表视图

- 查看网表,可以知道设计最终通过门级实现的情况。

- 状态机图

- 查看状态机图可以核对状态跳转图是否与自己的设计一致。

随笔小知识

- 执行时序分析的前提是工程完成了分析和综合(Analysis & Synthesis)、适配(Fitter)

- 芯片面积大,不利于降低成本和功耗

- always块中:if/else有优先级、case无优先级。注:casex有优先级

- 流水线pipeline把最长路径截断;流水线有几级,就有几个组合电路

- verilog中的x是给仿真用的

- 在always块中用的变量,一般定义为reg

- 组合和时序最主要的区别:有无D触发器

- 部分行为级代码不可综合,比如延时

#100,要想可综合需要改成RTL级,加入D触发器来达到延时的目的 - 三段式:输入组合电路、中间时序电路、输出组合电路。【分析的关键:找出D触发器,分出组合/时序】

- primitive:原语,比如or/xor/and等门电路

- 设计的时候,组合电路给真值表;时序电路给状态转换图。

- Mealy输出取决于当前状态和输入;Mealy机不跟时钟走,反应快

- Moore占资源多

- 竞争冒险的本质:同一信号经过不同路径,最后汇聚产生。

- 约束:延迟、扇出、引脚绑定、时钟频率

- 组合反馈环路的延时未知,一般在电路中不允许出现

- D触发器(DFF)和Latch(锁存器)区别,DFF是边沿型的,Latch是电平型的

- FPGA擅长乘除移位,不擅长矩阵求逆、三角函数。三角函数求解一般用查找法。

$同样无法综合,仿真时候用的- 时序电路,看见8个状态,想到3个D触发器, 2 n 2^n 2n的关系。

- 如果always后面的敏感信号列表用的是边沿型信号(比如clk信号的上升沿),且信号使用非阻塞赋值“<=”,那没有else会综合生成DFF;如果always后面的敏感信号列表用的是电平型信号,且信号使用阻塞赋值“=”,那没有else会综合生成latch;第二种一般是应该避免的,因为这种写法一般是希望生成组合电路,把else加上就好。

文章来源: recclay.blog.csdn.net,作者:ReCclay,版权归原作者所有,如需转载,请联系作者。

原文链接:recclay.blog.csdn.net/article/details/109775646

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)