【ZYNQ学习之FPGA开发】零、ZYNQ硬件初探

【摘要】

ZYNQ All Programmable SoC

赛灵思(Xilinx)推出的新一代全可编程片上系统,它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可...

ZYNQ All Programmable SoC

- 赛灵思(Xilinx)推出的新一代全可编程片上系统,它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

- ZYNQ旨在为视频监控、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。这款基于ARM处理器的SoC可满足嵌入式系统的高性能、低功耗和多核处理能力等要求.

SoC概念

- 一个芯片上实现一个系统的功能

- 与板上系统相比,SoC的解决方案成本更低,能在不同的系统单元之间实现更快更安全的数据传输,具有更高的整体系统速度、更低的功耗、更小的物理尺寸和更好的可靠性。

SoC发展

- 基于ASIC的SoC

- 可编程片上系统(SOPC,System-on-Progammable-Chip)

- 在FPGA部分实现ARM处理器

- 全可编程片上系统(APSoC,All-Programmable SoC)

- 硬核ARM处理器

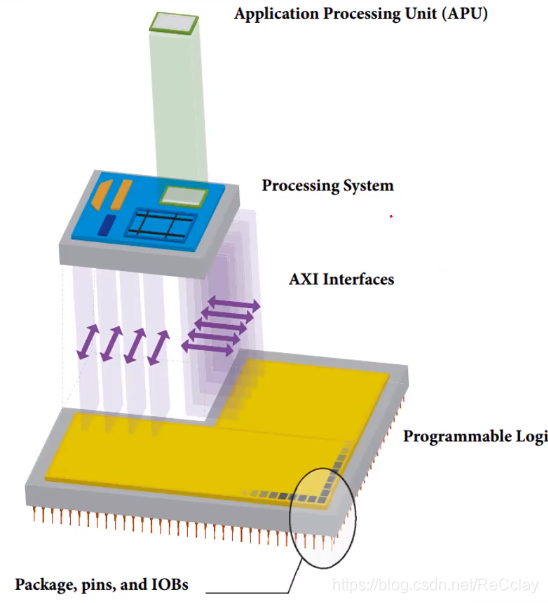

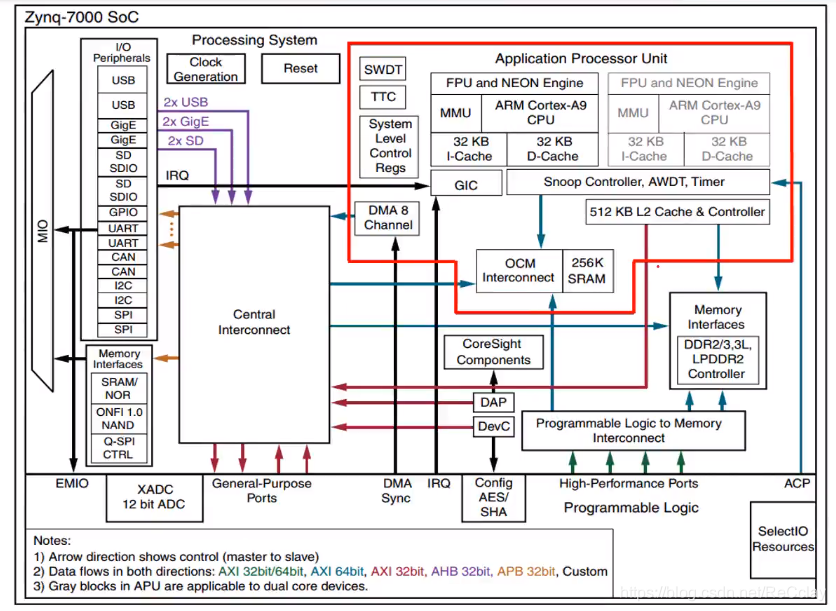

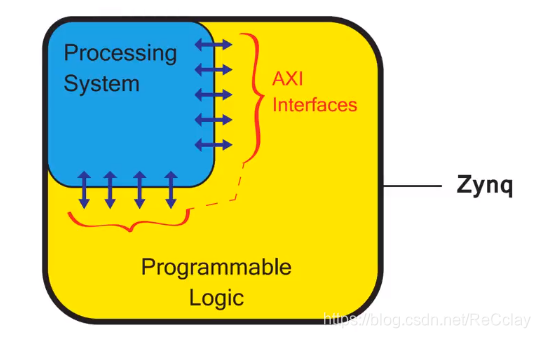

ZYNQ组成

- PS(Processing System)

- ARM处理器端

- PL(Programmable Logic)

- FPGA部分

- 性能 Artix < Kintex,如下图

PL

- PLD(Programmable Logic Device)可编程逻辑器件

- PLD内部的电路结构可以通过写入编程数据来设置

- 写入PLD的编程数据还可以擦除重写。即,PLD逻辑功能刻有使用者通过编程来设定

- 常用的PLD

- CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件

- 基于乘积项的与或逻辑阵列

- FPGA(Field Programmable Gare Array)现场可编程门阵列

- 基于查找表(LUT,Look Up Table)的CLB阵列

- FPGA定义:一种可通过编程来修改其逻辑功能的数字集成电路。

- CPLD与FPGA本质差异:电路结构不同

- CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件

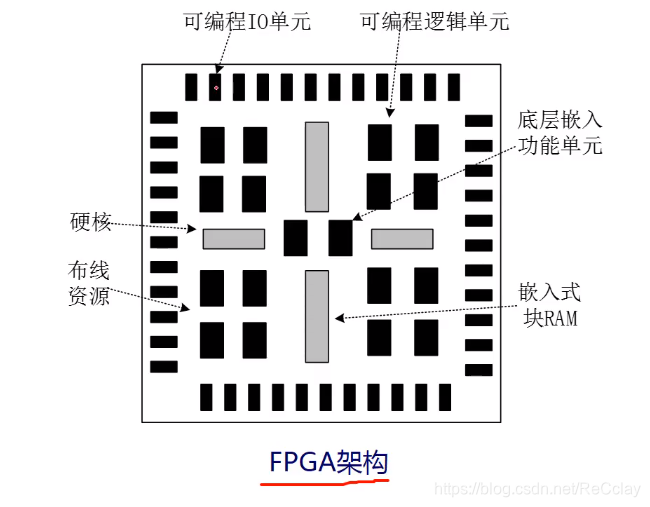

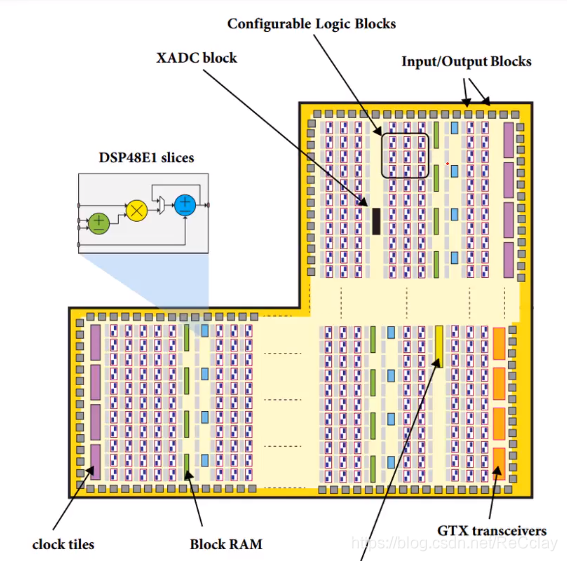

FPGA的架构

更详细的内部

- 可编程IO单元

- 可编程逻辑单元 - 如前面提到的CLB

- 底层嵌入功能单元 - 如PLL、DSP

- 嵌入式块RAM(Block RAM)

- 布线资源

- 硬核 - 有的有,有的没

PS部分

Vivado简介

- 类似Quartues

- 支持Block Design、Verilog、VHDL等多种设计输入方式

- 内嵌综合器以及仿真器

- 可以完成从设计输入、综合适配、仿真(通常也可以借助第三方仿真软件modelsim)到下载的完整FPGA开发流程

- 集成HLS(High Level Synthesis)工具,可以直接从高级语言生成硬件描述语言

Vivado开发流程(PL部分)

- 打开软件

- 新建工程

- 设计输入

- 如使用Verilog语言

- 分析与综合

- 语法检查、优化、转化为底层电路

- 约束输入

- IO约束(分配管脚)

- 时序约束(系统时钟、对于高速设计才需要添加)

- 设计实现

- 生成和下载比特流(bit - 用来下载程序)

调试利器

- ILA核(Integrated Logic Analyzer)

- 监控逻辑内部信号和端口信号

- VIO核(Virtual Input/Output)

- 实时监控和驱动逻辑内部信号和端口信号

文章来源: recclay.blog.csdn.net,作者:ReCclay,版权归原作者所有,如需转载,请联系作者。

原文链接:recclay.blog.csdn.net/article/details/105200985

【版权声明】本文为华为云社区用户转载文章,如果您发现本社区中有涉嫌抄袭的内容,欢迎发送邮件进行举报,并提供相关证据,一经查实,本社区将立刻删除涉嫌侵权内容,举报邮箱:

cloudbbs@huaweicloud.com

- 点赞

- 收藏

- 关注作者

评论(0)