【SoC FPGA学习】二、SoC FPGA硬件初探,基础扫盲

一、SOC FPGA基础介绍

SOPC介绍

- SOC FPGA之前的产品,软核ARM处理器(FPGA制作的处理器,占用FPGA资源,主频较低,但是可以释放该资源)

- NIOS II + FPGA通过Avalon MM 以及 Avalon ST总线进行通信

SOC FPGA定义

- 同一个芯片集成了FPGA和高性能的硬件逻辑固化的处理器HPS(Hardware Processor System)

- 不做他用,也不能释放该部分资源

SOC FPGA所用芯片

- Cyclone V SoC FPGA型号:5CSEBA2U19I7

- 主频高达925MHz,一般运行在800M

- Xilinx ZYNQ 7020具体型号: xc7z020clg400-2(放在这里仅做对比使用)

- 主频667~800M

SOC FPGA用到的软件

- Quartus Prime 17.1 【FPGA开发:需掌握新建文件、保存编译、分配引脚等基本操作】

- Platform Designer(原名叫Qsys)集成在Quartus 【重点掌握,为SOC FPGA添加外设(IP)、总线的连接、配置HPS各种参数、 DDR3 存储器参数配置等】

- SOC EDS (类似cmd)【只是一个终端】

- DS-5 AE(类似keil)【应用程序开发在这里进行】

- Modelsim(做FPGA仿真用)

SOC FPGA软硬件开发难点

- 硬件开发:Platform Designer中如何添加外设,如何连线。

- 软件开发:Linux驱动程序开发

- 驱动开发常常有现成的驱动框架,添加修改内容即可(读、写、控制等)

- 驱动开发主要针对PFGA侧添加的自定义进行的驱动开发(初始化寄存器)

Intel PSG(原ALTER)

- Cyclone V

- Cyclone V SE/SX 包含硬核

- Cyclone V E不包含硬核

- Arriva V

- Arriva 10

常用文件含义

- rbf:二进制数据流文件

- sof:编程文件

二、GHRD(黄金硬件参考设计)

下面会用到

Quartus软件,可参考开发板光盘下的<Quartus II 17.1 安装和许可指导书>,如下图所示。当然了,SoC EDS也在这个文档中,这个也是以后要用到的软件,可以一并进行安装!

2.1、GHRD概念介绍

GHRD(黄金硬件参考设计)

- 原厂模板工程,在该工程中已经针对DEMO板上的各种硬件外设添加好了对应的控制电路,并分配好了引脚,使用时只需在该参考设计中添加或修改自己所需的工作即可,可大大减少了工作量

- AC501在开发板光盘下的:

Demos\SOC_FPGA\Quartus\AC501_SoC_GHRD即为本开发板对应的GHRD工程,如下图所示。

<注意>:工程不能在中文路径下!!!

2.2、GHRD工程介绍

可以点击该工程下对应的AC501_SoC_GHRD.qpf文件,快速打开工程,如下图所示

在Quartus的左上方有个Project Navigator,双击其中的AC50_SoC_GHRD(v文件),即可打开Verilog代码,如下图所示。

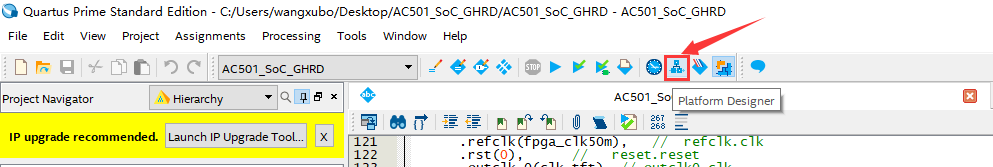

在工程的工具栏右侧倒数第四个即为Platform Designer,单击即可打开,如下图所示

注意,会让选择要打开的文件,这里选择soc_system.qsys文件,如下图所示

打开完成后界面,如下图所示

Platform Designer 菜单命令列表介绍

Qsys 界面介绍

2.3、GHRD的IP核介绍

在System Contents中可看到SOC FPGA总共有如下外设(IP):【选中某个外设在左侧通过按钮可以调节上下位置】

- clk_0(Clock Source)

- 默认添加,将外部时钟输入

- 设置时钟频率可以自动生成时序约束文件(运行在较高频率);其他IP核的参数会与该时钟频率相关,比如串口波特率分频器的时钟。

- hps_0(Arria V/Cyclone V Hard Processor System[altera_hps 17.1])

- 硬核ARM处理器 【最重要!】

- sysid_qsys(System ID Peripheral)

- 向系统贴标签,方便调试时知道系统对应的版本【操作方法:双击该外设,外右侧弹出的Parameters界面中的32 bit System ID中输入即可】

- led_pio(PIO【Parallel I/O】)

- led对应IO

- 右键选择其中Edit,可以进行编辑

- button_pio(PIO【Parallel I/O】)

- 按键对应IO

- uart_0(UART【RS-232 Serial Port】)

- 串口控制器

- spi_0(SPI(3 Wire Serial))

- SPI控制器

- clock_bridge_0(Clock Bridge)

- 从外部接时钟信号到内部

- alt_vip_vfr_tft(Frame Reader)

- 驱动显示屏用的

- 分辨率和总线宽度是基本要知道的参数

- alt_vip_itc_0(Clocked Video Output)

- 将Frame Reader读到的数据配合相应的时序,能够将读到的数据合理地送到显示屏的每一个点上!

- i2c_0(oc_iic)

- I2C控制器

各个外设显示界面如下图所示(下图将总线进行了折叠,关闭再打开Platform Designer后,折叠即可恢复为原来的样子)

各个外设更详细介绍可参考教程中的以下章节:

2.4、各个IP核与HPS连接关系

接下来分析,各个IP核如何是与ARM(HPS)连接到一起的。

1、时钟信号

首先来分析时钟信号,筛选信号操作如下,在Platform Designer下的System Contents界面下的筛选按钮,如下图

然后选择Filter中的Clock and Reset Interfaces选项,

选择完毕后关闭Filter,在System Contents界面即可看到各个IP之间的时钟关系,如下图(当然了想把某个IP往上调,也可以按System Contents界面左侧的箭头)

可以看到,clk_0的clk表示主时钟,提供给每个IP核使用,如下图所示(看其中加粗的黑线)

当然了,还有一个时钟桥clock_bridge_0输入的时钟信号(66M),它专门是显示屏读取数据用的,如下图

2、复位信号

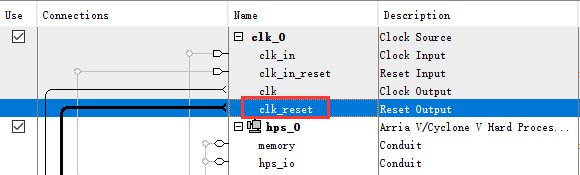

再来看复位信号,clk_0的复位信号与所有IP核的复位信号进行了连接,如下图所示

3、Avalon Memory Mapped slave

先在信号筛选器中,将筛选类型选择为All Interfaces,如下图所示

在其中的HPS_0的IP核中,其中的h2f_lw_axi_master(AXI Master),出来的信号连接到了各个IP核Avalon Memory Mapped slave上,如下图所示

那么h2f_lw_axi_master(AXI Master)核Avalon Memory Mapped slave到底是什么意思呢,接下来一一介绍。

首先来看h2f_lw_axi_master(AXI Master),在SOC FPGA中有三个桥,通过这三个桥,通过数据交换,三个桥分别是

- F2H_AXI_Salve(HPS是从机,数据由其他外设发起)

- H2F_AXI_Master(HPS是主机,数据由HPS发起)

- H2F_LW_AXI_Master(HPS是主机,数据由HPS发起)(lw的意思是low weight,表示轻量级的,寻址空间只有2M字节,性能较低(但是控制uart,I2C完全足够了))

注:其中的Master核Salve是站在HPS的角度来说的

H2F_LW_AXI_Master通过虚拟地址映射这个比较简单!

把F2H_AXI_Salve这个桥用起来是SoC FPGA这个架构的优势所在!

2.5、添加一个timer外设

如何添加一个IP外设,拿一个timer举例,步骤如下:

①、在IP Catalog中搜索timer,然后双击其中的Interval Timer

②、接着弹出如下配置窗口,这里这是为了举例如何添加,故先不修改配置,直接默认即可,如下图

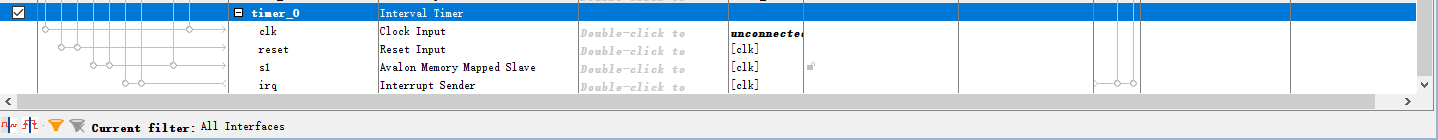

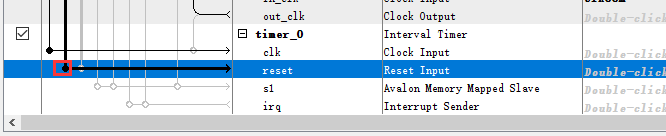

添加完成后,在System Contens的最下面即可看到

③、接下来便是连接timer这个IP核的信号了。

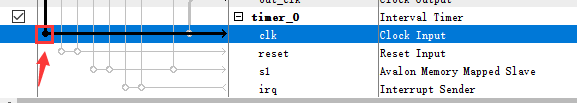

首先是时钟信号,注意要与F2H_LW_AXI_Master的时钟信号保持一致!如下图

添加时钟的方法,先选中目标时钟,如上图。然后再单击本信号时钟与目标时钟的交汇点,如下图

接着连接复位信号,这里直接连到了clk_0这个IP核的clk_reset,如下图

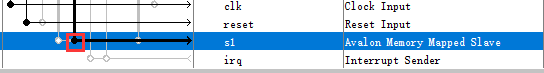

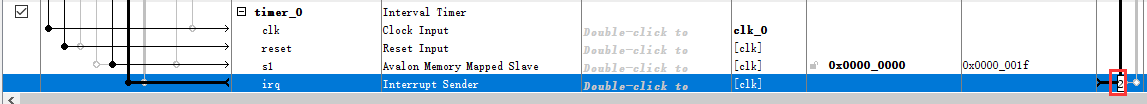

s1对应的Avalon Memory Mapped slave连接到hps_0的h2f_lw_axi_master即可,如下图

最后一个IRQ信号

2.6、深入了解HPS

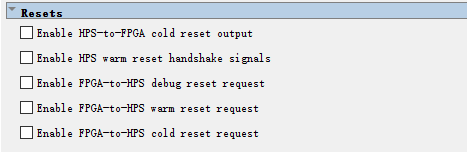

在hps_0模块右键点击Edit,在FPGA Interfaces板块下的General先不用管,属于高级选项。

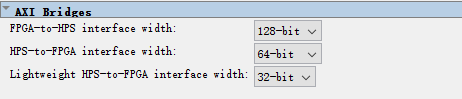

AXI Bridges是设置三个桥的宽度(当没有用到某个桥的时候,可以选择unused关闭【性能、功耗有所优化】)

针对FPGA需要用到SDRAM时配置(FPGA使用HPS部分的SDRAM接口),直接点击+号即可创建

复位,暂时高级用的不用管。

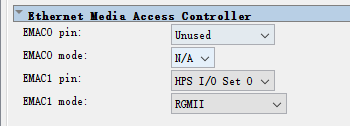

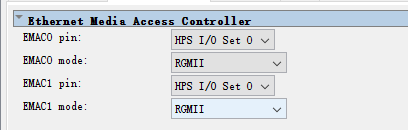

IO口复用,在其中的Peripheral Pins栏

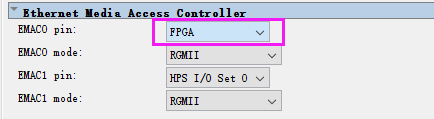

以Ethernet Media Access Controller(太网控制器)为例

将其中的EMAC0 pin选择为HPS I/O Set 0

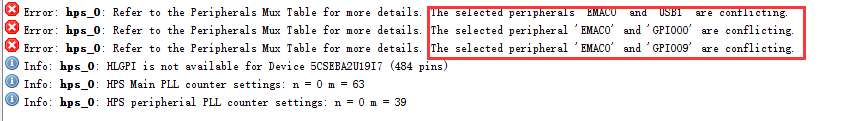

但是会发现报错,如下图,可以大概知道是EMAC0其它功能公用管脚,造成冲突了!

往下滑动,可以看到具体的复用。红色部分表示以太网使用的的引脚,蓝色部分为USB使用引脚,紫色部分为GPIO0和GPIO9使用到的引脚,可以发现明显冲突了!

假若我现在硬要使用以太网控制器,如何办呢?选择FPGA,即分配到FPGA部分的管脚上,通过FPGA管脚引出!

可以发现没有错误提示了,点击右下角的Finish,回到Platform Desigener界面,可以看到hps_0下增加了相应的EMAC信号,如下图

接下来双击,将其导出

然后点击菜单栏的Generate->Show Instantiation Template…

以上是千兆以太网分配到FPGA侧进行设计,I2C、UART等也是可以这样设计的!

三、SoC FPGA 开发流程简介

SoC FPGA 设计包括以 ARM Cortex-A9 处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、 IDE 环境的软件设计、软件调试等。 SoC FPGA系统设计的基本软件工具包括:

- Quartus Prime, 用于完成 SoC 系统的分析综合、硬件优化、适配、配置文件编程下载以及硬件系统测试等;

- Platform Designer(原名 Qsys) ,它是 HPS 硬核处理器的开发包,用于实现HPS 系统配置、生成以及与 HPS 系统相关的监控和软件调试平台的生成;

- ModelSim, 用于对 Qsys 生成的基于 HPS 组件的 HDL 描述语言程序进行系统功能仿真;

- SoC EDS,这是厂家针对 SoC FPGA 芯片专门开发定制的一个工具, 该工具类似一个 Linux 虚拟机,包含了很多通用或专用的工具, 支持 Linux 系统中常用的各种命令如 cd、 ls、 chmod、 cat、 make, 也包含了一些专用的工具, 如用于生成 dts 文件的 spocdts 工具、 用于生成 Altera 专属的 preloader 头文件用的mkpimage 工具,用以烧写 uboot 和 preloader 文件到 sd 卡中用的 alt-boot-diskutil 工具等等。 使用 SoC EDS, 可以针对特定的硬件工程生成相应的 uboot 源码并编译得到 uboot 镜像文件,也可以实现对 Linux 应用程序、内核和驱动的编译。即在不安装 Linux 操作系统的情况下,就能完成基于 HPS 系统的软件开发和调试。

SoC FPGA 的开发流程通常包括 2 个方面: 基于 Quartus II、 Platform Designer 的硬件设计, 基于 SoC EDS 和 DS-5 的软件设计。对于比较简单的SoC 应用系统,一个人便可执行所有设计;对于比较复杂的系统,硬件和软件设计可以分开进行。

3.1、硬件开发

硬件开发使用 Quartus Prime 和 Platform Designer。 硬件设计工作如下:

- (1)、在 Platform Designer 软件中添加 HPS 组件以及各外围器件(如片内存储器、 PIO、 定时器、 UART、 片外存储器、 DMA 等), 并定制和配置它们的功能;分配外设地址及中断号;设定复位地址;最后生成系统。 也可以添加用户自定义外设以实现定制功能, 减轻 CPU 工作负担。

- (2)、使用 Platform Designer 生成含 HPS 的系统后, 会得到一个.qsys 后缀的文件, 将其集成到整个 Quartus Prime 工程中。 然后可以在 Quartus Prime 工程中加入 qsys 系统以外的逻辑, 大多数基于 SoC FPGA 的设计都包括 Qsys 系统以外的逻辑, 这也是基于 SoC FPGA 器件的系统优势所在。 用户可以将 HPS 高性能处理器和具有强大并行处理能力的 FPGA 高度整合,以得到最佳的性能。

- (3)、使用 Quartus Prime 软件来选取具体的 SoC FPGA 器件型号; 然后为系统分配引脚, 对于 HPS,主要是设置 SDRAM 的引脚电平和 IO Bank 电平。另外还要根据要求进行硬件编译选项或时序约束的设置; 最后编译 Quartus Prime 工程, 在编译过程中 Quartus Prime 将对 Qsys 生成系统的 HDL 设计文件进行布局布线, 从 HDL 源文件综合生成一个适合目标器件的网表, 生成 FPGA 配置文件(.sof)。

- (4)、使用 Quartus Prime 编程器和 Intel FPGA 下载电缆(如 USB Blaster), 将配置文件(用户定制的含 HPS 系统的硬件设计)下载到目标板上。当校验完当前硬件设计后,可将新的配置文件下载到目标板上的非易失存储器里(如EPCS 器件)。下载完硬件配置文件后,软件开发者就可以将此目标板作为软件开发的初期硬件平台进行软件功能的开发验证了。

3.2、软件开发

软件开发主要使用到两个工具, SoC EDS 和 Intel FPGA 部门深度定制的DS-5 软件。

SoC EDS 是 Intel 部门专门开发的 SoC EDS 软件,这是厂家针对 SoCFPGA 芯片专门开发定制的一个工具, 该工具类似一个 Linux 虚拟机,包含了很多通用或专用的工具, 支持 Linux 系统中常用的各种命令如 cd、 ls、 chmod、cat、 make, 也包含了一些专用的工具, 如用于生成 dts 文件的 spocdts 工具、 用于生成 Altera 专属的 preloader 头文件用的 mkpimage 工具,用以烧写 uboot 和preloader 文件到 sd 卡中用的 alt-boot-disk-util 工具等等。 使用 SoC EDS, 可以针对特定的硬件工程生成相应的 uboot 源码并编译得到 uboot 镜像文件,也可以实现对 Linux 应用程序、内核和驱动的编译。即在不安装 Linux 操作系统的情况下,就能完成 Linux 软件开发和调试。其主要特性包括:

由 Intel FPGA 部门深度定制的 DS-5 软件可以用来编写、 编译、 调试 SoC芯片不含操作系统的裸机程序, Linux 内核和驱动模块,该软件包含以下特性:

- 基于易用的 Eclipse 编辑器

- 支持 GCC 编译器编译和调试 Linux 应用程序

- 支持调试 Linux 内核和驱动模块

- 支持使用 USB Blaster 调试 ARM 处理器

- 支持 FPGA 和 ARM 交叉触发联合调试

- 支持优化软件的 profile 特性

使用 SoC EDS 配合 DS-5 软件, 可完成基于 HPS 处理器系统的所有软件开发任务。使用 Platform Designer 生成系统后, 就可以使用 SoC EDS 来生成和编译 HPS 系统的 Bootloader 程序了,然后使用 DS-5 软件开始设计 HPS 裸机应用程序或基于 Linux 系统的 C/C+ +应用程序代码。 而且针对 Platform Designer 中提供的很多 IP 核, 如 PIO、 UART、 SPI、 DMA、 Frame Reader 等, Linux 系统中都提供了相应的驱动源码, 使用时仅需配置 Linux 内核以支持这些设备驱动,再编译得到内核镜像,使用该镜像启动,就能自动识别并添加这些设备到系统中了(需要对应的设备树文件的配合)。

3.3、总结

SoC开发流程

- 修改Platform Designer 中的设计,添加IP(最终生成文件格式是.qsys)

- 重新集成Qsys系统文件到Quartus中(如添加外设PIO UART SPI)

- 设定信号的IO管脚(落实到具体的IO口),全编译

- 得到sof(肯定得到)或者rbf(rbf可选,Linux配置FPGA会需要!)

- 通过编译还会生成soc_system.sopcinof文件,包含了在Platform Designer中设计的硬件信息。

- 若单纯基于虚拟地址映射编程,需要依据soc_system.sopcinof文件生成hps_0.h

- 若想在linux中自动设备添加IP,驱动、设备,能够使用文件IO编程的话,需要依据soc_system.sopcinof文件生成soc_system.dts,进一步处理得到socfpga.dtb

什么时候修改dtb,什么时候修改uboot

- 对于DTB文件来说,只要在Platform Designer中进行了任何修改,都需要soc_system.dts,进一步处理得到socfpga.dtb

- 对于preloader和Uboot来说,在Platform Designer修改了HPS组件的参数

编译配置保存内核

- 内核位于 /home/xiaomeige/linux-socfpga

- 加载已有的内核配置: make scofpga_defconfig

- 打开内核配置的图形界面:make menuconfig

- 保存配置好的内核信息:make savedefconfig && mv defconfig arch/arm/configs/×××

切换到root用户:su,然后输入密码

切花到普通用户:su ×××,

生效交叉编译器环境变量路径:source /home/xiaomeige/.profile

设置目标架构:export ARCH=arm

设置具体的编译工具链:export CROSS_COMPILE=arm-linux-gnueabihf-

开始编译内核:make 生成zImage(在内核源码的arch/arm/boot目录)

文章来源: recclay.blog.csdn.net,作者:ReCclay,版权归原作者所有,如需转载,请联系作者。

原文链接:recclay.blog.csdn.net/article/details/105164906

- 点赞

- 收藏

- 关注作者

评论(0)