【紫光同创PGL22G学习】三、以PLL为例,学习IP core使用

导读:在很多 FPGA 芯片内部都集成了 PLL,其他厂商可能不叫 PLL,但是也有类似的功能模块,通过 PLL 可以倍频分频,产生其他很多时钟。本实验通过调用

PLL IP core来学习 PLL 的使用方法。

一、实验原理

PLL(phase-locked loop),即锁相环。是 FPGA 中的重要资源。由于一个复杂的 FPGA 系统往往需要多个不同频率,相位的时钟信号。所以,一个 FPGA 芯片中 PLL 的数量是衡量 FPGA 芯片能力的重要指标。FPGA 的设计中,时钟系统的 FPGA 高速的设计极其重要,一个低抖动, 低延迟的系统时钟会增加 FPGA 设计的成功率。

本实验将通过使用 PLL, 输出一个方波到开发板上的扩展口 J8 的 PIN3 脚,来演示使用PLL 的方法。

数字锁相环(PLL):主要由鉴频鉴相器( PFD,Phase FrequencyDetector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator) 等组成。通过不同的参数配置,可实现信号的调频、调相、同步、频率综合等功能。 LogosPLL 的电路框图如下图所示:

二、PLL IP core使用

(1)点击 Tool 菜单下的 IP Compiler。

(2)再在弹出的界面里选择 PLL 下的 Logos PLL,再对 PLL 取名 clk_wiz_1,然后单击 Customize。

(3)在 Basic Configurations 界面里, 勾选复位管脚使能"Enable Port pll_rst",输入的时钟频率为50Mhz。输出选择 clk_out0~clk_out3 四个时钟的输出,频率分别为 200Mhz, 100Mhz, 50Mhz,25Mhz(注意勾选 Enable)。这里还可以设置时钟输出的相位,我们不做设置,保留默认相位。

(4)点击左上角 Generate 按钮生成 PLL IP 的设计文件,生成成功后会弹出是否添加到工程的对话框,选择Yes

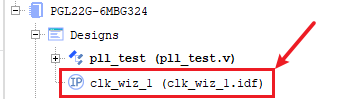

(5)这时一个 clk_wiz_1 IP 会自动添加到我们的 pll_test 项目中, 用户可以双击它来修改这个 IP 的配置

(6)我们再来编写一个顶层设计文件来实例化这个 PLL IP, 编写 pll_test.v 代码如下。

module pll_test(

input sys_clk,

input rst_n,

output clk_out ,

output locked //pll clock output J8_Pin3

);

clk_wiz_0 clk_wiz_0_inst

(

.clkin1(sys_clk), // IN 50Mhz

.clkout0(), // OUT 200Mhz

.clkout1(), // OUT 100Mhz

.clkout2(), // OUT 50Mhz

.clkout3(clk_out ), // OUT 25Mhz

.pll_rst(~rst_n), // RESET IN

.pll_lock(locked)

);

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

程序中先用实例化 clk_wiz_1, 把单端 50Mhz 时钟信号输入 sys_clk 到 clk_wiz_1 的 clkin1,把 clk_out3 的输出赋给 clk_out。

- sys_clk 为 50MHz 的系统时钟

- rst_n 为复位信号

- clk_out 为 PLL 输出的 25MHz

- locked 为波形稳定输出锁定

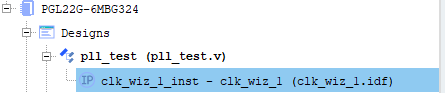

(7)保存工程后,pll_test 自动成为了 top 文件,clk_wiz_1 成为 Pll_test 文件的子模块。

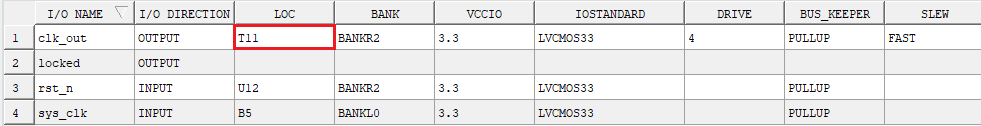

(8)再为工程进行管脚约束

文章来源: recclay.blog.csdn.net,作者:ReCclay,版权归原作者所有,如需转载,请联系作者。

原文链接:recclay.blog.csdn.net/article/details/115058827

- 点赞

- 收藏

- 关注作者

评论(0)