MC9S12XS128 事件处理

MC9S12XS128 事件处理

一、复位

1.1 上电复位(Power-On Reset )

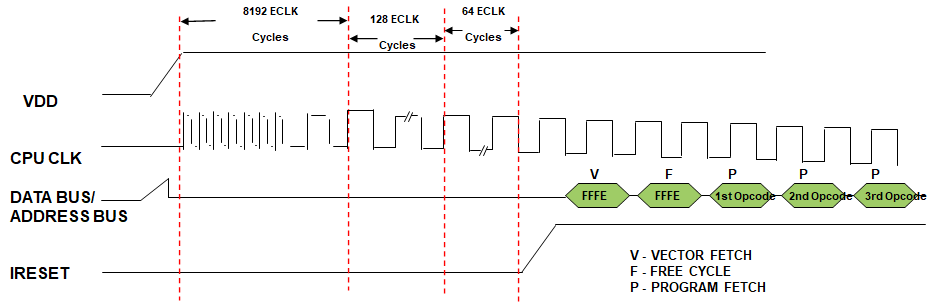

在 S12 的 VDD 引脚上的一个正向变化将触发上电复位,当给 S12 上电时,它以一个已知的、确定的设置启动,具体启动流程如下图

- 首先 VDD 有一个正跳变初始化

- 然后 CPU 经历 8192 个 E-clock 延时保持晶振的稳定

- CPU 内部软件复位,启动系统

如果VDD上升缓慢,到延时结束时尚未到达MCU的额定工作电压,那么退出POR开始工作就可能出现无法预料的结果,特别是片内EEPROM的安全,在混乱中如果意外被改写,将造成系统信息的丢失

1.2 外部复位(External Hardware Reset )

为了解决上面的问题,S12配备一个标记为 /RESET 的低电平有效复位引脚,系统在上电阶段让 /RESET 引脚保持足够长时间的有效电平,与电压联系起来,确保电压达到额定值后再释放该引脚,而在掉电阶段则通过监视电源电压,确保低于额定值前让/RESET有效,强迫MCU进入复位状态从而停止运行,当该引脚电压为低时,触发复位

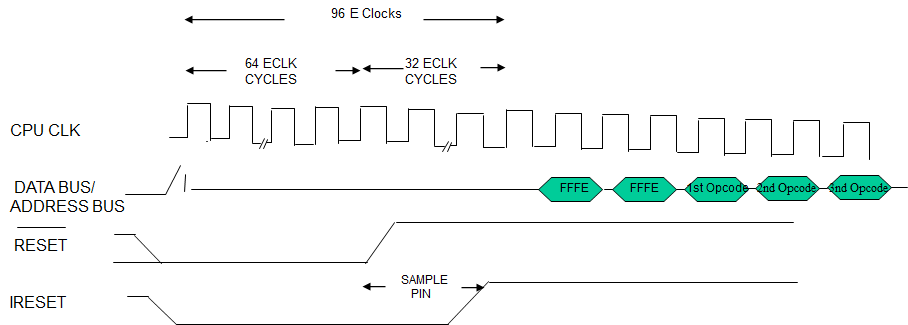

简单的 RC 延时复位电路在里面不能使用,因为 MCU 内部还有 COP 和时钟监视电路这两个复位源,它们复位MCU 时也会将/RESET引脚拉低,并随后释放,而MCU必须依靠该引脚状态判断复位源,然后转向不同的入口。事实上一旦出现复位条件,内部电路就会将/RESET拉低64个E时钟周期,随后释放,再过32个E时钟周期,从内部采样/RESET引脚,如果仍然是低电平,CPU就认为是外部复位;如果回到高电平,就表明是内部复位。如果外加RC电路,内部拉低/RESET引脚并释放后,由于电容充电延迟效应,其电平很难保证在32个E时钟周期内恢复到高状态,于是就可能导致MCU错误判定复位源

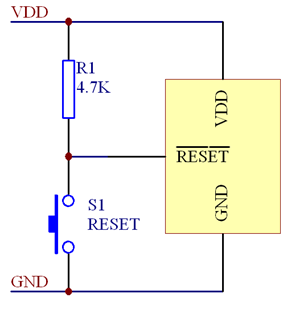

复位我们可以使用下面的复位电路

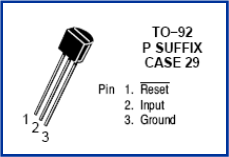

使用三极管如下:

注意:上电复位和RESET引脚复位共用一个复位向量 $FFFE ~ $FFFF,必须确保该矢量指向工作程序入口

1.3 计算机工作正常复位 (Computer Operating Properly)

COP 系统允许 S12 检测软件执行故障。通常,COP在软件开发过程中是关闭的。这是一项重要的安全保障功能。COP系统包含一个用户设置的倒计数定时器。若定时器过期,则触发一个系统复位。为了防止定时器过期,执行的程序必须在倒计数定时器失效前向ARM/RESET COP定时器寄存器(COPRST)中写入 $55 和 $AA,他通常有另外一个称呼:看门狗,如果不在设定的周期内喂狗,就会引发系统软件复位

COP复位的矢量地址是 $FFFA ~ $FFFB,他必须在超时前被服务,其有一个控制寄存器如下:

COPCTL - COP 控制寄存器($003C)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| 功能 | WCOP | RSBCK | 0 | 0 | 0 | CR2 | CR1 | CR0 |

| 复位 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

-

WCOP - Window COP Mode

1 : Window COP operation

0 : Normal COP operationCOP可以运行在普通模式或者Window模式,在window操作模式下,软件必须服务COP在选择的超时周期的最后25%;如果软件企图写入ARM 的 COP寄存器在 window 之外,COP将产生复位

-

CR[2:0]

COP 看门狗定时器超时时间间隔

ARMCOP - COP 复位寄存器($003F)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

为了防止定时器过期,执行的程序必须在倒计数定时器失效前向 ARMCOP定时器寄存器(COPRST)中写入 $55 和 $AA,写入除 $55 和 $AA 以外的任何内容都使MCU立即复位

1.4 时钟监控复位(Crystal Monitor )

CPU 内部集成了时钟监视器,它专门负责监视系统时钟是否正常,如果时钟频率跌到预定值以下,它就会强制系统复位,这同时也等于为 MCU 限定了一个最低工作频率,当系统选用的时钟频率过低时,时钟监视器也会动作。复位后时钟监视器默认为关闭状态,如果确实需要在低速度下工作,可以不启动它

时钟监视器复位的矢量地址是 $FFFC ~ $FFFD,其优先级仅低于上电复位

PLLCTL — CRG PLL 控制寄存器($003A)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| CME | PLLON | FM1 | FM0 | FSTWKP | PRE | PCE | SCME |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

- CME——Clock Monitor Enable

1 = 允许时钟监控功能

0 = 禁止时钟监控功能 - SCME——Self-Clock-Mode Enable

1 = 检测到晶振时钟失效,MCU进入自时钟模式;

0 = 检测到晶振时钟失效时,引起时钟监控复位

二、中断

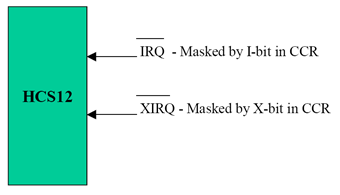

2.1 /XIRQ非屏蔽中断

XIRQ 是非屏蔽中断引脚,无论MCU处于哪种运行状态,该引脚一旦被拉成低电平,MCU执行完当前指令后,都会响应该中断,中断矢量为 $FFF4 ~ $FFF5,该中断一般用于系统掉电、硬件故障等重要场合,当MCU处于等待或暂停模式时,该中断将唤醒MCU

2.2 非法指令陷阱

MCU 正常工作时,每次取址得到的都是由汇编或编译程序生成的有效操作码,MCU能够正确解释并执行它们,但当受到干扰或系统出现混乱时,可能得到无法识别的操作码,即非法指令,这时MCU自动产生一次中断,中断矢量地址为 $FFF8 ~ $FFF9

2.3 软件中断指令 SWI

SWI 是一条指令,但其执行过程与中断相同,即通过中断矢量确定目标地址,中断矢量为$FFF6 ~ $FFF7,它自动保存 MCU 的寄存器和返回地址,最后必须通过RTI指令返回

2.3 中断现场保护

在进入中断的时候,系统会进行一次中断现场保护,中断保护就是保存当前程序的入口地址,以及运行的寄存器环境到堆栈,具体保存的内容如下:

| 序号 | 堆栈地址 | 入栈内容 | 说明 |

|---|---|---|---|

| 1 | SP - 2 | RTNH:RTNL | 保存中断返回地址 |

| 2 | SP - 4 | YH:YL | 保存变址寄存器Y |

| 3 | SP - 6 | XH:XL | 保存变址寄存器X |

| 4 | SP - 8 | B:A | 保存累加器B:A(D) |

| 5 | SP - 9 | CCR | 保存程序状态字CCR |

中断响应前,堆栈必须有效,SP必须指向一个有效的RAM区,而且堆栈的大小必须不少于9个字节

2.4 中断寄存器

2.4.1 INTCR — 中断控制寄存器($001E)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| IRQE | IRQEN | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

IRQE - Interrupt Select Edge Sensitive

- 1 = IRQ PIN is configured for negative edge

- 0 = IRQ PIN is configured for level sensitive

IRQEN - External IRQ Enable

- 1 = IRQ PIN is connected to interrupt logic

- 0 = IRQ PIN is disconnected from interrupt logic

2.4.2 HPRIO — 高优先级设定寄存器($001F)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| PSEL7 | PSEL6 | PSEL5 | PSEL4 | PSEL3 | PSEL2 | PSEL1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

该寄存器用于将某个可屏蔽中断的优先级 “ 推进 ” 为可屏蔽中断的最高可能中断,复位后该寄存器默认值为 $F2,则IRQ( $FFF2,$FFF3)中断在可屏蔽中断中的优先级最高

- 写入HPRIO中的中断向量的后八位,可以改变中断的优先级

- 优先级的作用只有在多个中断源同时请求中断时在能体现

2.4 中断优先级

一般来说,不可屏蔽中断比可屏蔽中断的优先级高,上面我们提到的几个优先级的顺序如下:

RESET > 时钟监控复位 > COP 看门狗复位 > 非法指令陷阱 > 软件中断指令(SWI) > XIRQ

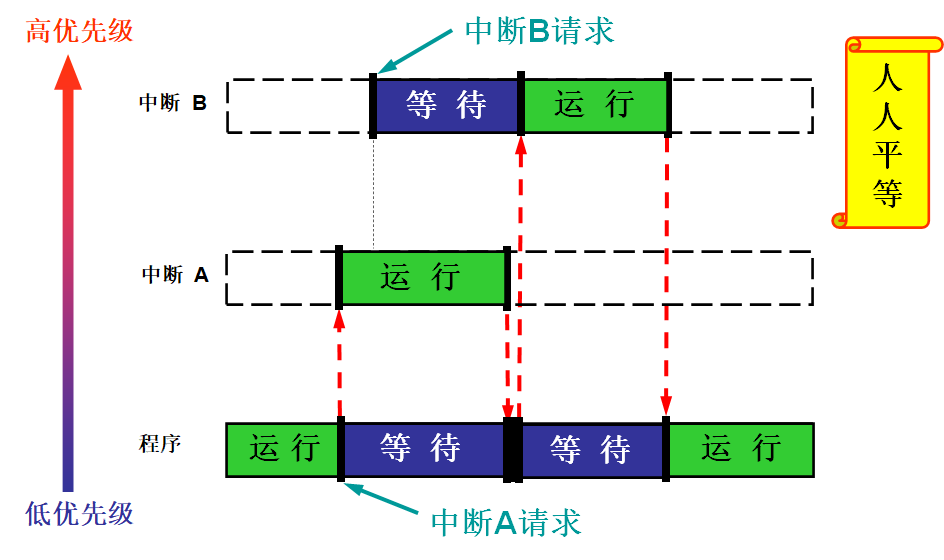

中断响应的三种状态

- 默认状态:

- 在进入中断服务程序时,I位自动置1,禁止其他可屏蔽中断

- 即使有优先级更高的中断请求,必须等当前中断服务程序执行完以后才能响应

- 优先级的作用只有在多个中断源同时请求中断时才能体现

- 无法实现中断嵌套

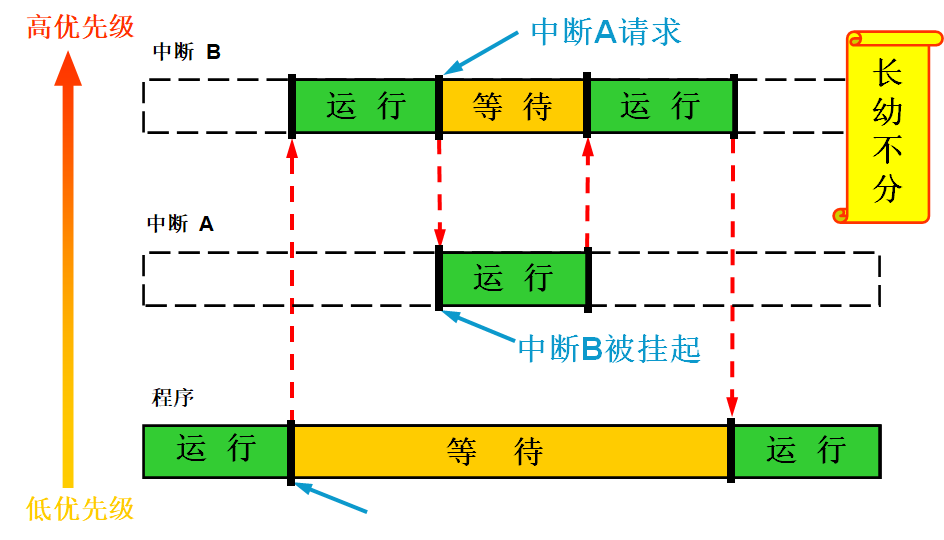

- 中断嵌套状态

- 在进入中断服务程序时,手动对I位清零

- 任何其他可屏蔽中断都可以被响应,无论其优先级有多高

-

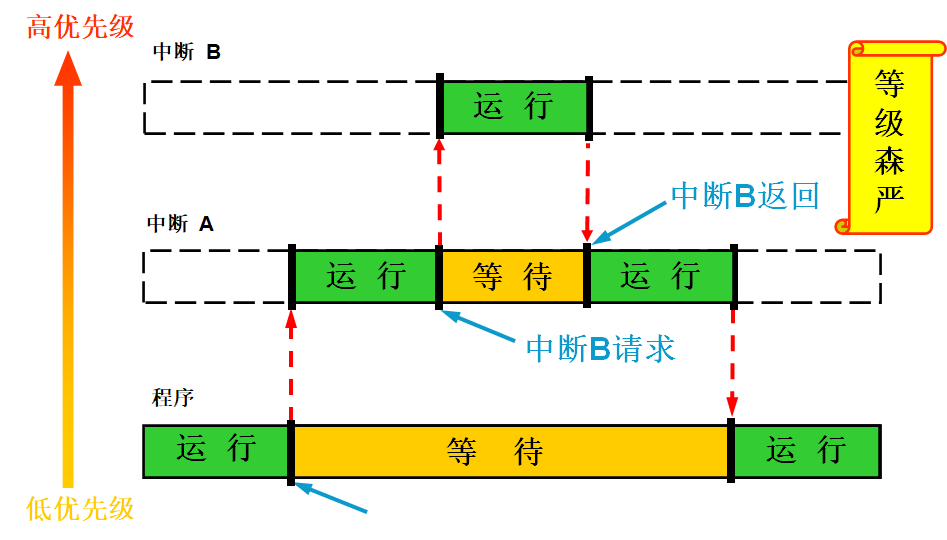

中断优先处理机制

与上面中断处理机制不同的是,低优先级的中断可以被高优先级响应

开启优先处理机制的方法

- 在中断服务程序中,首先对 I 清零,即EnableInterrupts

- 选择优先级更高的中断源可以进入响应中断

- 设置优先等级

| 优先等级 | 设置方式 |

|---|---|

| 两级 | 一个中断源为低优先级,其他为高优先级 在低优先级中断服务程序中,对 I 位清零 在高优先级中断服务程序中,不清零 |

| 多级 | 利用局部的中断屏蔽位 比如Timer Channel0 的中断屏蔽位 TIE_C0I |

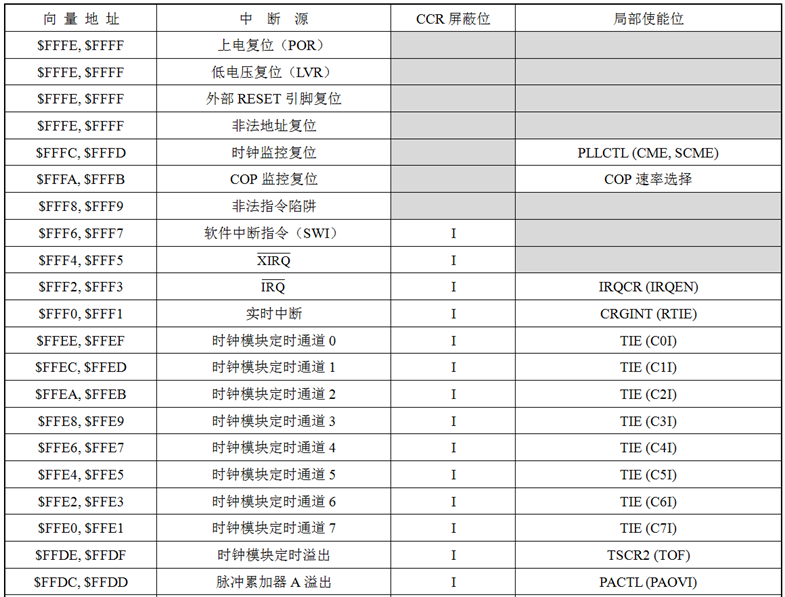

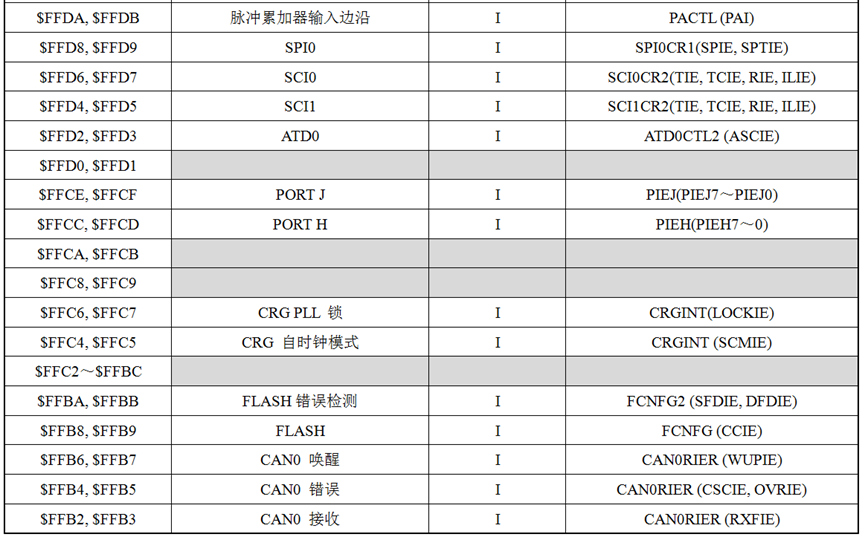

2.5 中断向量表

中断向量表是中断源的识别标志,可用来 形成相应的中断服务程序的入口地址或存放中断服务程序的首地址称为中断向量,默认的向量表如下:

文章来源: blog.csdn.net,作者:JeckXu666,版权归原作者所有,如需转载,请联系作者。

原文链接:blog.csdn.net/qq_45396672/article/details/120589524

- 点赞

- 收藏

- 关注作者

评论(0)